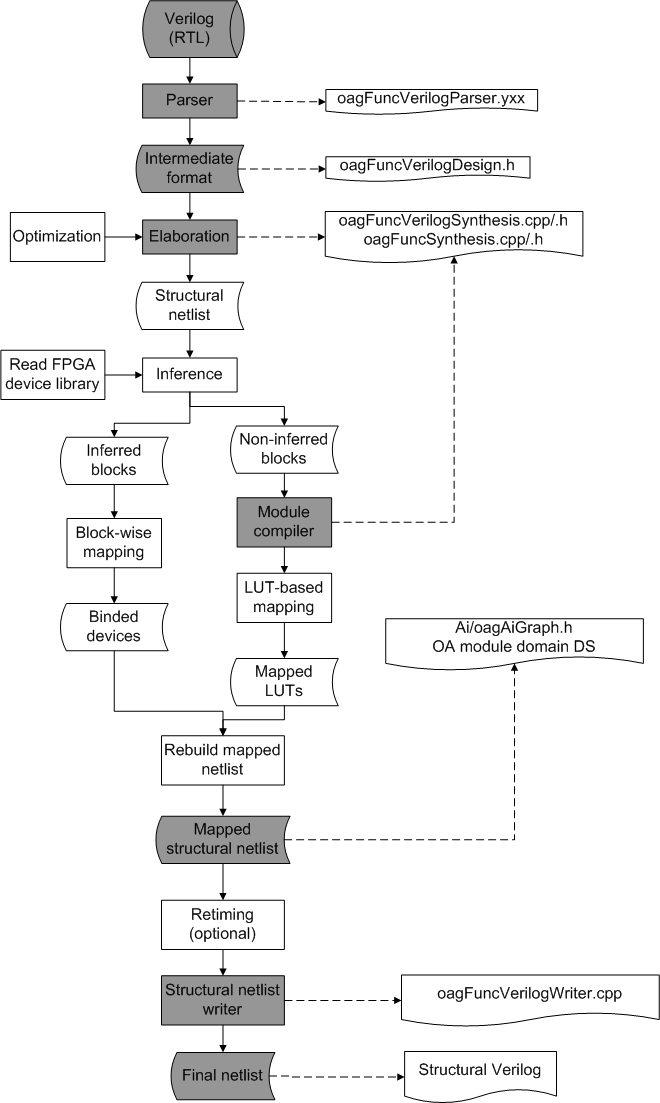

Verilog Parser: A simple but powerful enough Verilog parser is

implemented in OAGear. The main feature in Verilog language that is not

implemented in this parser is the handler for loop statements (indicated by

for/while). A good thing is that the structure of this parser

is very easy to understand so that the update is not difficult. The Verilog

grammar and handler have been implemented in oagFuncVerilogParser.yxx.

TODO: handle the missing features in Verilog in the parser.

Intermediate Format: The internal

representation after parsing a Verilog format is a direct reflection of the

original Verilog structure. Basically they are a linked-list of modules,

within each of which a sequence of statements/blocks are contained. The data

structure of OAGear's IF can be found in file oagFuncVerilogDesign.h.

TODO: create the corresponding data structure for loop statement.

Elaboration and Module Compiler: The

basic idea of OAGear RTL synthesizer is to convert a behavioral Verilog to

an AND-INVERTER graph (AIG), which is a logic level netlist with only AND2

gates and inverters. In this sense, there is no inference procedure during

the whole RTL synthesis flow in OAGear since the existing synthesizer in

OAGear is essentially technology-independent. In OAGear, synthesizer's

Elaboration and module are basically combined together and the

implementation can be found in oagFuncVerilogSynthesis.cpp/.h and

oagFuncSynthesis.cpp/.h. The implementation strategy in module compiler is

detailed in its documentation (located in "Documentation" subdirectory under

"Func" directory).

TODO: In the general RTL synthesis flow, we need the structural

netlist which preserves the original flavor of the Verilog RTL description

instead of decomposed logic level description since certain information,

such as arithmetic operations, is lost in lower level representation.

Thereby a separation between elaboration and module compiler is needed. To

enable this separation, a data structure that represents the structural

netlist after elaboration and before inference should be designed.

Structural Netlist Writer.

OAGear has implemented a simple netlist writer to output the AIG based logic

level design to a structural Verilog file. All registers are represented by

a always block.

TODO: To support different FPGA vendor's back-end tool, various

structural netlist writers for different output formats (e.g., EDIF or XNF)

are desired.

What Is Missing. All white blocks are the missing parts in OAGear Verilog synthesizer to build a complete RTL synthesizer. Systematically, we have to implement the following major building blocks.

- Elaboration and optimizations during it.

- Inference (partial mapping) and FPGA device library manager.

- LUT-based mapping (in fact we can use the technology mapper implemented in "$OAGear_HOME/mapper").

To enable the bridge between 1 and 2, a data structure that represents the structural netlist after elaboration and before inference should be designed.