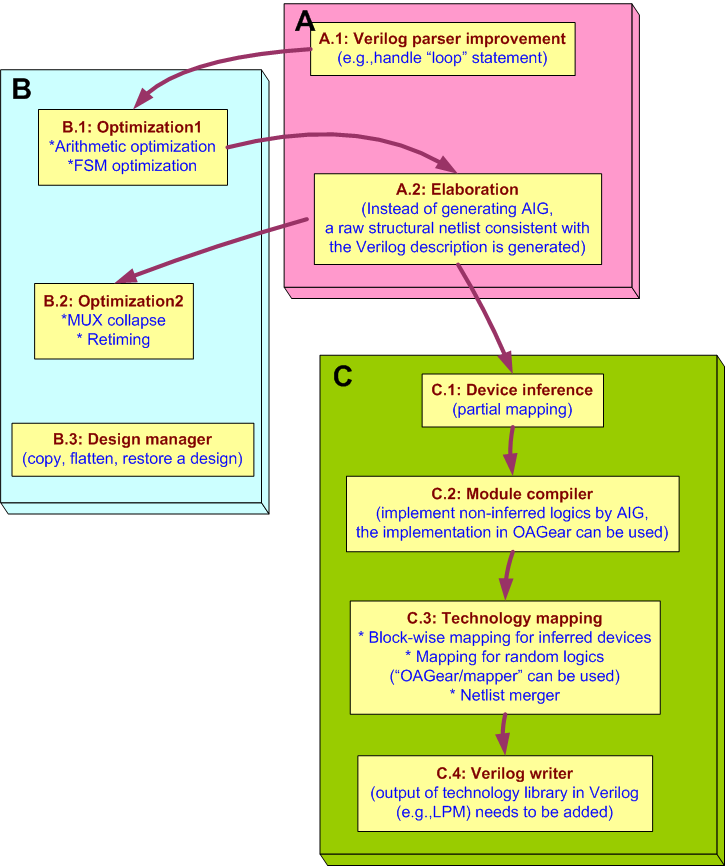

System partition diagram

Estimated work labor, priority for each tasks:

| TaskID |

Esti-labor (hours*person) |

Priority |

| A.1 | 20+ | low |

| A.2 | 60 | high |

| B.1 | 40 | low |

| B.2 | 40 | low |

| B.3 | 40 | medium |

| C.1 | 20 | high |

| C.2 | 20 | high |

| C.3 | 30 | high |

| C.4 | 10 | medium |

Suggested tasks partition:

| TaskID | Person in Charge |

| A | Yu Hu |

| B | Zhe Feng |

| C | Zhipeng Liu |

Some comments:

Task A: I've been working on the front-end Verilog parser and elaboration for a while, therefore I'd like to continue working on this line so that I can get it done quickly and then help others.

Task B: Optimization and design management are optional tasks for a complete RTL synthesis flow but they are essential distinguisher for a good RTL synthesizers. Hence the priorities of these tasks are low while they may need lots of thinking and long implementation time.

Task C: The mapping part requires strong background on FPGA devices and Verilog language. In this sense, I think that Zhipeng should be the best one. Although there are more blocks in task C compared to task A and B, most of them have been implemented or partially implemented in OAGear, such as module compiler, random logic technology mapping and Verilog writer. Thereby, the most jobs left are device inference and integration of netlist outputed by different routines.