# Collective Computational Activity in Self-Assembled Arrays of Quantum Dots: A Novel Neuromorphic Architecture for Nanoelectronics

Vwani P. Roychowdhury, Member, IEEE, David B. Janes, Member, IEEE, Supriyo Bandyopadhyay, Senior Member, IEEE, and Xiaodong Wang

Abstract—We describe a new class of nanoelectronic circuits which exploits the charging behavior in resistively/capacitively linked arrays of nanometer-sized metallic islands (quantum dots), self-assembled on a resonant tunneling diode, to perform neuromorphic computation. These circuits produce associative memory effects and realize the additive short-term memory (STM) or content addressable memory (CAM) models of neural networks without requiring either large-area/high-power operational amplifiers, or massive interconnectivity between devices. Both these requirements had seriously hindered the application of neural networks in the past. Additionally, the circuits can solve NPcomplete optimization problems (such as the traveling salesman problem) using single electron charge dynamics, exhibit rudimentary image-processing capability, and operate at room temperature unlike most quantum devices. Two-dimensional (2D) processors, with a 100 × 100 pixel capacity, can be fabricated in an area of 10<sup>-8</sup> cm<sup>2</sup> leading to unprecedented functional density. Possible routes to synthesizing these circuits, employing self-assembly, are also discussed.

### I. INTRODUCTION

T is widely believed in the solid state device community This widely believed in the solid strategies for integrating devices on a that conventional strategies for integrating devices on a device because chip will be impractical for nanoelectronic devices because of their small size (~100 nm), low power handling capacity and low gain. Accordingly, many new proposals have been advanced, articulating primarily, visions of future architectures for nanoelectronic circuits [1]-[10]. Some of these proposals, which contemplate building Boolean logic circuits using Coulomb interaction between bistable charge polarizations in quantum dots are flawed [5]. They have overlooked the fact that bistability is a necessary, but not a sufficient condition for implementing Boolean logic circuits. Individual logic devices must also have isolation between the input and output (as in a conventional transistor) so that the input drives the output and not the reverse. Coulomb interaction between two identical charge polarizations is reciprocal so that it is impossible to distinguish the "input" polarization from the "output" po-

Manuscript received April 29, 1996. This work was supported in part by the U.S. Army Research Office under Grants DAAH04-95-1-0586 and DAAL03-G-0144, and by the U.S. National Science Foundation under Grant ECS 9 308 814.

Publisher Item Identifier S 0018-9383(96)07213-9.

larization (i.e., there is no isolation between the input and output). In other words, the output influences the input just as much as the input influences the output! Consequently, logic signal cannot propagate unidirectionally from the input to the output, or from one stage to the next, leading to total failure [6], [7], [11]. The failure occurs because the input cannot uniquely (and predictably) determine the output. This problem is pathological in many proposed schemes of nanoelectronic architecture. Other proposals, which advocate the use of cellular automata architectures with local connectivity [1], also have shortcomings; they offer no mechanism for loading the initial program into the cellular array of quantum devices [11]. As a result, they are also of questionable efficacy. Recently, a scheme, based on the precise phase-locking of single electron tunneling oscillations in capacitively coupled nanojunctions to realize the parametron computing model of von-Neumann and Goto, has been proposed [10]; but it seems to lack fault-tolerance. Finally, some recent proposals for dissipationless computing [4], although quite intriguing, can hardly be considered practical since they have no errorcorrecting capability. Added to all this is the fact that most of these schemes make unreasonable demands on materials and fabrication technology that cannot be met in the near future.

In [6], [8], and [9], we proposed a radically different scheme for nanoelectronic architecture that suffers from none of the drawbacks just discussed. It has a number of unusual features. First, we realized that any proposal, which requires extreme fabrication tolerance whereby billions of nanoelectronic devices must be fabricated on a wafer with nominally identical behavior, is unrealistic. There will always be stochasticity in a large-scale system (e.g., a complex computer or signal-processing chip) and it may be wiser to exploit this stochasticity to realize useful functions rather than strive against it. This is precisely what we do. Second, we insist on room temperature operation since cryogenic operation is impractical. Finally, we restrict attention to niche applications where the collective (and sometimes stochastic) activity of a large number of nanostructure devices, working in unison, gives rise to useful computational activity.

The architecture that we implement is inspired by standard models of neural networks. It is massively parallel and inherently fault-tolerant. Moreover, it has significant fabrication tolerance (a 100% variation in the size of an individual device is quite tolerable) and a great deal of noise immunity. The

V. P. Roychowdhury, D. B. Janes, and X. Wang are with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA.

S. Bandyopadhyay is with the Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556 USA.

relative insensitivity to size variation accrues from the fact that the size determines the capacitance of an individual device. A 100% variation in the size of an individual device will result in a similar variation in the capacitance and this does not affect the performance of the circuit as a whole very much because of the "collective" nature of the computation. Here the collective activities of all devices acting cooperatively matter, rather than the characteristic of a single device. The switching speed of every device is  $\sim 1$  ps and the power delay product can approach the fundamental thermodynamic limit of  $kT \ln 2$  [12] which is less than  $10^{-20}$  Joules. Needless to say, all of these are very desirable features.

This paper is organized as follows. In the next section, we describe a prototype nanoelectronic network fashioned from a 2D array of metallic islands self-assembled on the surface of a double barrier resonant tunneling diode structure. This very simple system produces associative memory effects, realizes the short-term additive memory (STM) or content addressable memory (CAM) model of neural networks, performs 2D image processing and solves NP-complete combinatorial optimization problems. Examples of all this are provided in Section III. In Section IV, we discuss possible techniques for fabricating the network. Finally, in Section V, we provide the conclusions.

# II. A SELF ASSEMBLED ARRAY OF METALLIC ISLANDS ON A RESONANT TUNNELING DIODE: A NEUROMORPHIC CIRCUIT

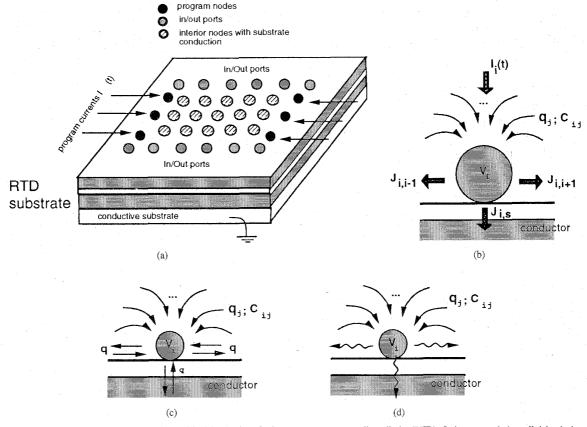

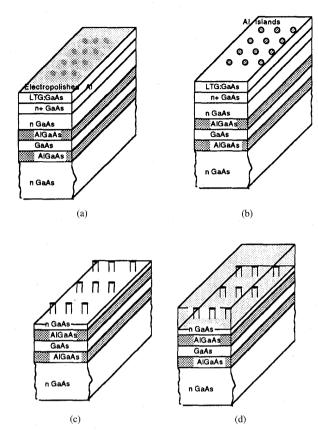

In the past, many proposals for nanoelectronic circuits advanced ideas that could not be implemented in practice using technology that is either presently available or is likely to be available in the near future. In contrast, the basic array of circuit nodes in our proposed system can be fabricated with relative ease. The primary technology required to produce our circuits is a technology to create a 2D periodic array of nanometer-sized metallic islands (with nearest neighbor interconnections) on a substrate whose current-voltage characteristic has a nonmonotonic nonlinearity. Individual islands can have a diameter between 10 and 100 nm depending on the application. Such a structure is shown in Fig. 1(a). The nearest-neighbor interconnects are implemented by organic molecular wires or some other suitable means. This is an established technology and the details of the fabrication will be given in Section IV. The substrate can be a resonant tunneling diode (RTD) whose conduction characteristic has the required nonmonotonic nonlinearity [13]. All our circuits utilize this basic structure. We assume that the molecular wires or other interconnections between the metallic islands can produce a variety of different network mechanisms (e.g., phase-coherent, or ohmic, or nonlinear, or single-electron, or rectifying transport, etc.) which lead to a rich plethora of circuit functions. Some of these possible network mechanisms are depicted in Fig. 1(b)-(d).

Electrically coupled arrays of nanometer scale metallic islands, comparable to that depicted in Fig. 1(a), have been fabricated in the past using self-assembly [14]. There is experimental evidence that one can establish inter-island conductive and capacitive links between the nanometer sized metallic islands with organic molecular wires [14]. Single

electron charging effects and nonlinear transport have been demonstrated in these systems at room temperature [15]. Furthermore, self-assembled buckytubes may also realize the interconnects [16], [17]. Additionally, there is experimental evidence that phase-coherent links may prevail between metallic spheres which have been embedded in a porous dielectric matrix [18]. Therefore, a wide variety of transport mechanisms can be realized at present which provides an adequate degree of design flexibility.

The final requirement for realizing the complete system shown in Fig. 1(a) is a suitable scheme for reading and writing data. In the topologies described in Section III, each circuit node must be addressed individually. Present interconnect technology is not capable of providing individual connections at this density, although advances in nanometer scale patterning or self-assembly techniques may provide such capabilities in the near future. In the shorter term, related computational topologies with somewhat reduced functionality can be realized with all input/output ports and program nodes at the periphery of the chip. In that case, all input/output are provided to or retrieved from a few selected nodes at the periphery or edge of the chip. An architecture based on such "edge-driven" paradigm is represented by the general structure proposed in Fig. 1(a). A scheme that can implement logic functions using such a structure has been recently proposed. The interconnect problem is greatly simplified in the "edgedriven" case, since it is necessary to externally access only those islands that communicate with the external world. Of course, conventional bonding technology will not be adequate to access these islands because it does not possess the resolution needed to address individual quantum dots. In fact, typical bonding pads will probably consume the area occupied by about 10 000 islands. Therefore, we need a contact technology capable of virtually atomic resolution. The obvious choice is a scanning tunneling microscope (STM) tip which has been shown to be capable of such resolution [19]. They can also read the voltages on the island. STM tips were proposed for input/output data lines in [6] which visualized an array of tips micromachined into a wafer and permanently attached to input/output ports for data reading and writing. Attaching an STM tip to an individual dot may be accomplished using fine line direct-write lithography followed by metallization. This is a difficult step and significant developmental work should precede implementation. Recently, the operation of an integrated 100 micron size STM fabricated on a chip by standard lithography was demonstrated by Hitachi Research Laboratories [20] which is an important advancement in this direction. It should be noted that the size of the dots in our proposed structures is typically 10 nm so that once the STM tips are correctly attached, thermal drift or vibration is no longer a problem. Additionally, one should note that direct write lithography is being used only for making contacts to the chip and not for delineating the quantum dots or the interconnects between them. Therefore, the throughput will not be unacceptably slow even though direct write lithography is used. Recent work on arrays of scanning tunneling microscope tips, in which each tip has been individually addressed [21] lends further credence to this idea.

Fig. 1. A generic array of nanometer-sized metallic islands deposited on a resonant tunneling diode (RTD). It is assumed that all islands have direct conductive/capacitive links to their nearest neighbors established, for example, via organic molecular wires. These wires are not shown for the sake of clarity. A subset of the islands serve as program nodes that are driven by external current sources. Another subset of islands serve as input/output ports, and the remaining islands introduce complexity to the system through nonmonotonic nonlinear conductive link to the substrate; (b)–(d) Cross-sectional view showing island i, whose potential  $v_i$  is influenced by the charges  $q_j$  in the rest of the network through a capacitance matrix. Continuous charge dynamics (where electric charge is a classical continuous variable) is depicted in (b). An analogous system governed by single electron dynamics (charge is a discrete variable) is depicted in (c). Dynamics of networks with quantum links (in which charge transport is phase-coherent) is depicted in (d).

The choice of the system in Fig. 1(a) was motivated by the observation that complex spatial and temporal patterns of the electronic charge distributions on the metallic islands, resulting from the nonlinear interactions amongst thousands of devices (islands) which are collectively driven far from equilibrium by currents applied at the program nodes, may reveal a fundamental kind of computational effect [22]. Indeed, we will show in Section III that this system is tailor made for neuromorphic computation and signal processing.

# III. SPECIFIC EXAMPLES OF NEUROMORPHIC NETWORKS USING QUANTUM DOT ARRAYS

In this section, we will provide specific examples of useful computational or signal processing functions performed by the generic array of electrically linked nanometer sized metallic islands shown in Fig. 1(a). We will consider, primarily, memory-like circuits which operate on the basis of neuromorphic principles. It is possible to establish a connection between neuromorphic computational models and the charge dynamics in an array of metallic islands, in the presence of each of the different network mechanisms indicated in Fig. 1(b)–(d). For example, when the operation of the network is governed by

single-electron effects at each island [see Fig. 1(c)], the choice of a neuromorphic approach is motivated by a straightforward comparison between the granular dynamics of electrons in an array of islands, and the dynamics of discrete Hopfield networks [23]. We will illustrate this in Section III-C with a specific example. Additional impetus for restricting attention to memory applications comes from the realization that single-electron charging dynamics is stochastic in nature, which hinders the conceptualization of logic applications. Associative memory, on the other hand, can benefit from an appropriate kind of stochasticity.

#### A. Neuromorphic Continuous Charge Network

The first example of neuromorphic networks we consider is a purely classical example where the islands in Fig. 1(a) are large enough (diameter  $\sim 100$  nm) and the temperature high enough that single electron effects are not prominent. Charge can be considered a continuous (rather than discrete) variable and the corresponding network mechanism is illustrated in Fig. 1(b). A one-dimensional (1D) version of the circuit is shown in Fig. 2 in which we assume that the current between islands i and j is  $J_{ij}$ , and that the current between island i

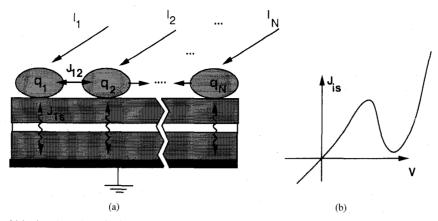

Fig. 2. (a) A 1D array of islands, whose dynamics is described by (2); (b) a nonmonotone substrate nonlinearity of the kind shown here, is the minimal condition for the realization of collective effects. This characteristic can be produced by a resonant tunneling diode.

and the grounded substrate is  $J_{is}$ . Since charge is considered a continuous variable, we can write from Kirchoff's current balance condition that

$$\frac{d}{dt}q_i = C_i \frac{d}{dt}v_i$$

$$= -\left[J_{is}(v_i) + \sum_{j \neq i} J_{ij}(v_i - v_j)\right] + I_i(t) \qquad (1)$$

where  $I_i(t)$  is the driving current,  $q_i$  is the charge,  $v_i$  is the potential, and  $C_i$  is the capacitance, with the subscript i indicating the relevant island,  $J_{is}$  is a nonmonotonic nonlinear function of  $v_i$  corresponding to the current-voltage characteristic of an RTD.

1) Operation as an Associative Memory: Qualitatively, the multiple solutions to the nonlinear system of equations which results from (1) under steady-state conditions  $(dv_i/dt=0)$  for all i) will be taken as a set of memory states which can be programmed by properly choosing the current biases  $I_i$ . The current biases  $I_i$  will be assumed to be either time independent, or slowly varying on time scales over which the network relaxes into its memory states. If the network is begun at time t=0, with a certain initial condition  $v_i=q_i/C_i$  for all i, arranged, for instance, by an initial impulse of charges  $q_i$  at each of the islands, then the network will evolve toward the closest memory state, as programmed by the current biases  $I_i$ . This is the functioning of an associative memory.

Equation (1) bears strong similarities to the equations representing the additive short-term memory (STM) (or Content Addressable Memory (CAM)) model of neural networks [24]. Therefore, it is obvious by analogy that the system in Fig. 2 realizes the STM or CAM model. The significant difference is that, while conventional circuit realizations of the STM model require operational amplifiers (whose transfer functions exhibit monotonic sigmoidal nonlinearities) and massively interconnected networks of resistors [24]–[26], all we need is an RTD as a substrate which provides a *nonmonotonic* nonlinearity in the local transport. In [8], we showed that this nonmonotonic nonlinearity is sufficient for the realization of associative memory effects. Op-amps are very costly in terms of real estate on a chip and also consume too much power. As

a result, neural networks have been unable to compete with conventional silicon VLSI technology. In contrast, RTD's are very compatible with low-power nanoelectronics. They can be integrated vertically beneath the array of islands so that they do not use up any real estate on the chip. There has been some prior research involving resonant tunneling diodes (RTD) for the realization of neuromorphic systems by Levy and co-workers [27]. Additionally, some early investigation of networks of tunnel diodes has been reported by Stern [28] and by Wilson [29], which also exhibit current-voltage characteristics of the kind shown in Fig. 2(b).

In [8], we proved two important results pertinent to this system. First, based on global stability analysis using Liapunov functions, we showed that the system in (1) is globally stable. This implies that there are no limit cycles, and that every trajectory of the system will converge to one of its equilibrium points. Second, we showed that nonmonotonic nonlinearities in the current-voltage characteristic of local transport, such as that shown in Fig. 2(b), are necessary to obtain multiple equilibrium points for nontrivial collective computational activity in these networks. It should be contrasted with the general requirement of monotonic nonlinearities in generic additive short-term memory systems [24]–[26] which is realized through op-amps. This result also has immediate consequences to nanoelectronics, in that staircase nonlinearities, which have been produced in quantum point contact constriction [30] and asymmetric double junction single electron tunnel devices [31] can be seen to be inadequate for the realization of collective activity. However, there are several electronic devices which can produce nonmonotonic nonlinearities, e.g., Esaki diode, IMPATT diode, BARITT diode, etc. [32]. We are interested chiefly in semiconductor heterostructure devices which can be integrated vertically beneath the array of islands. They must also be low power devices. Therefore, the ideal structure is a RTD. Since our work focuses on nanoelectronic realizations, complex circuitry cannot be integrated with the basic elements anyway owing to the small size of the islands. Therefore, an RTD seems to be the optimum choice.

We next provide numerical results based on particular choices of  $J_{ij}$ 's and  $J_{is}$ 's. Our first example is illustrated in Fig. 3(a), in which the two islands are coupled with each other

Fig. 3. (a) Two islands coupled by a resistor  $R_{12}$  and capacitor C. Each island is also coupled to the substrate by a capacitance  $C_0$  and a nonlinear resistor whose current voltage characteristic is given in (b); (b) Piecewise approximation to the nonmonotonic nonlinearity of the substrate conduction [cf. Fig. 2(b)]. This characteristic defines the quantities R and  $v_0$ . Each segment has the same magnitude of slope 1/R.

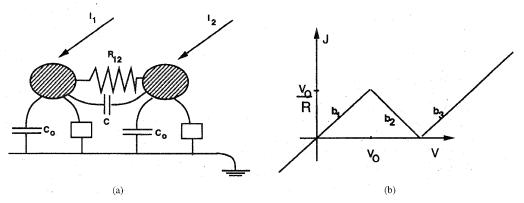

Fig. 4. Phase portrait for two-island system in the continuous-charge model, in which the voltage axes have been scaled with respect to  $v_0$ . The parameters are  $R_{12} = 5R$ , and  $I_0 = v_0/2R$ . (a) with only substrate capacitance  $C_0 = 2q/v_0$ ,, and (b) with identical mutual and substrate capacitances:  $C = C_0$ .

through a linear resistor  $R_{12}$  and a capacitor C. In addition, we assume that each island is individually coupled to the substrate through a capacitance  $C_0$ , and a nonlinear resistor whose current-voltage characteristic is shown in Fig. 3(b). Furthermore, each island is driven by a current  $I_o$  fed externally. Since the results presented here are numerical in nature, we have minimized the number of parameters by choosing a piecewise linear function to represent the I-V characteristic of the RTD (substrate conduction). Each of the three segments are given slopes of the same magnitude R

$$J_s(v) = \begin{cases} v/R & v < v_0 \\ (2v_0 - v)/R & v_0 \le v \le 2v_0 \\ (v - 2v_0)/R & v > 2v_0 \end{cases}$$

(2)

The equilibrium points of this two-node system can be found by setting  $\dot{v}_1=\dot{v}_2=0$ , and the stability properties of those equilibrium points can be ascertained by examining the eigenvalues of the system matrix near the equilibrium points [33], [34]. Provided that the driving current  $I_0 < v_0/R$ , each

island can in principle be on any one of the three branches of the nonlinear function  $J_s(v)$ . We can, however, show that the system will be unstable if either island is operated on branch  $b_2$ . So, it follows that this system can have at most four different globally stable points, since each island is restricted to being on either branch  $b_1$  or  $b_3$ . Two of these stable points are trivial ones corresponding to both islands operating on the same branch: either  $b_1$ , or  $b_3$ . We have determined a necessary and sufficient condition for the existence of all four "memories," and the corresponding phase portraits are shown in Fig. 4.

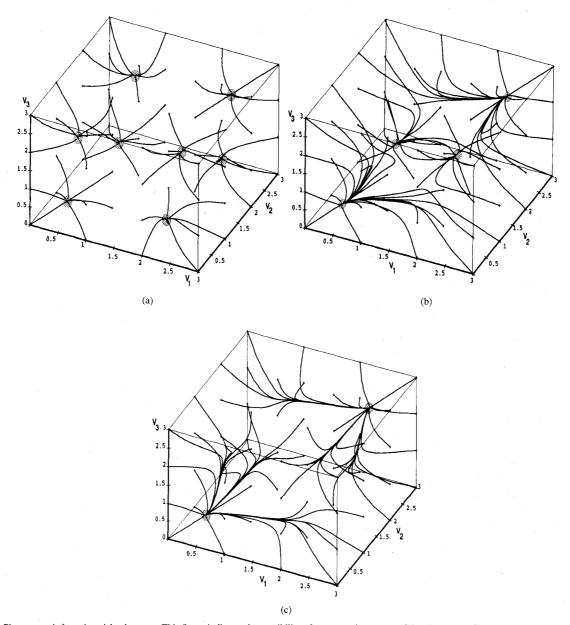

One can also realize *programmed* associative memory. An example is shown in Fig. 5 where different choices of interisland resistances lead to the occurrence of either eight, four, or two equilibrium points.

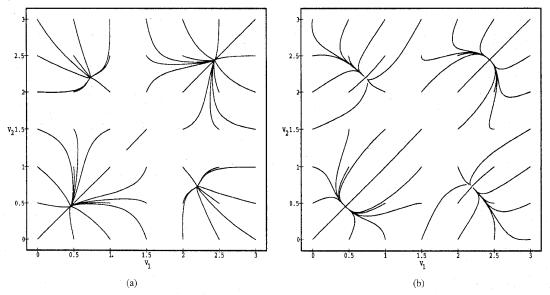

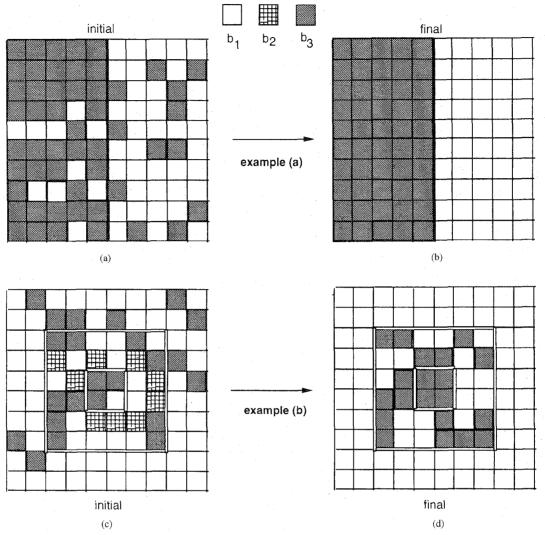

2) Image Processing Network: Fig. 6 shows results of further numerical investigations, where a 2D array of  $10 \times 10$  islands with only near-neighbor connections and the same substrate nonlinearity [as shown in Fig. 3(b)] are used. An

Fig. 5. Phase portrait for a three island system. This figure indicates the possibility of programming a network by choosing resistance parameters appropriately. Only substrate coupling  $C_0$  is permitted. The stable equilibrium points are indicated by the shaded circles. (a) eight states, with  $R_{12} = R_{23} = R_{13} = 10R$ , (b) four states, with  $R_{12} = R_{23} = 10R$ , and  $R_{13} = 5R$ .; (c) two states, with  $R_{12} = R_{23} = 5R$ .

input image is digitized to create dark and light pixels. Each pixel generates a voltage on a corresponding island. These voltages lie on a particular branch— $b_1,b_2$ , or  $b_3$ , in Fig. 3(b)—of the substrate nonlinearity. Dark pixels place the corresponding voltages on the branch  $b_3$ , light pixels on the branch  $b_1$  and intermediate grey pixels on the branch  $b_2$ . In example (a), the input contains domains which are either predominantly dark, or light, and the resulting output recovers domains which are either all dark, or all light. This is an example of "smoothing," an important image processing capability. Other image processing functions can be realized as well. We must point out that this  $10 \times 10$  network consumes an area of  $10^{-10}$  cm<sup>2</sup> so that ten trillion such image

processors can be fabricated within an area of 1 cm<sup>2</sup>. This is an unprecedented functional density.

## B. Single-Electron Charging Effects

We have also considered the same two-island network as in Section III-A, with the assumption that single electron charge effects (granularity of charge) have become pertinent either due to the lowering of temperature, or due to the physical scaling of the metallic islands down to  $d\sim 10$  nm. Single-electron effects will become relevant, when the change in potential  $\delta V=q/C$ , associated with the addition of a single electron charge q to an island, becomes comparable to kT/q, the thermal potential. This condition can be met even at room

Fig. 6. Rudimentary image processing capability in a near-neighbor connected network of  $10 \times 10$  islands, which are all pumped by the same current  $I_0 = v_0/2R$ . Each island is colored in accordance with the particular branch— $b_1,b_2$ , or  $b_3$ , in Fig. 3(b)—of the substrate nonlinearity, the island potential lies on. (a) The resistive network is uniform  $R_{i\pm 1,j\pm 1}=6R$ . The input contains domains which are either predominantly black, or white, and the resulting output recovers domains which are either all black, or all white. (b) The network is partitioned into three concentric regions. The islands in the outermost and innermost regions are coupled with low resistances  $R_{i\pm 1,j\pm 1}=3R$ , and the islands in the intermediate region are coupled with high resistances  $R_{i\pm 1,j\pm 1}=13R$ . Parts of the network with low resistance produce regions which are either all white, or all black depending on which was predominant in the initial state.

temperature if islands with an effective capacitance smaller than  $C\approx 5\times 10^{-18}$  F are fabricated.

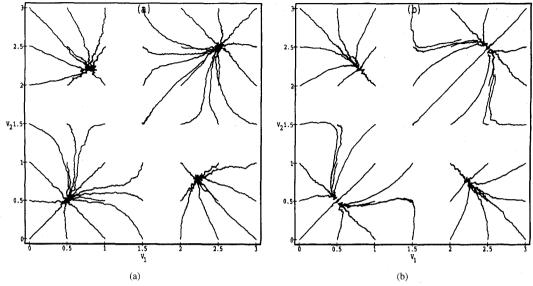

Single electron dynamics are characterized by discrete tunnel events. Therefore, the differential equation systems of (2) cannot be used to model the arrays. We developed a Monte-Carlo simulation technique [35], [36], for the simulation of a current biased network of islands, shown in Figs. 1 and 2. Owing to space limitations, we cannot describe it here, but instead refer the reader to [8].

The results based on our numerical simulator show the following:

1) For large enough values of the effective substrate capacitances  $(C_0)$ , the effect of the single electron dynamics is marginal and the system is adequately described by the continuous charge models. Thus even arrays of metallic islands with diameters of few nanometers can exhibit

- the same associative memory and image processing capabilities studied in Section III-A.

- 2) If the substrate capacitance is made smaller, the granularity of the trajectories become larger, and for small enough values, the phase portrait breaks out into oscillations [8].

These effects are illustrated in Fig. 7, where the same system shown in Fig. 3 is investigated under single-electron dynamics.

### C. Ising-Type Single-Electron Networks

The examples in Section III-A and III-B did not utilize single-electronics in a direct way, i.e., single electron charging effect was not central to the operation of the circuit. However, there are instances when single electronics plays a pivotal role. In [8], it was shown that the evolution of an initial charge distribution toward a stable final equilibrium distribution in a

Fig. 7. Phase portrait for the same two island system in Fig. 3 where the granularity of charge (single electron charging) has been taken into account. These results are obtained from Monte-Carlo simulation and are discrete charge versions of the two cases in—Fig. 4(a).

system of the type of Fig. 1(a) can be given a neuromorphic interpretation. These properties emerge *purely as a result of the discreteness of electronic charge*, and the only assumption made in establishing this connection is that the inter-island capacitances can be chosen arbitrarily.

In [8], it was shown that the discrete stochastic dynamics of electrons can be viewed as a procedure for simulated annealing. Consequently, several problems from combinatorial optimization can then be mapped to different single-electron networks. A novel mapping methodology tailored specifically for single-electron networks was developed. Owing to space limitations, we cannot address this in greater detail here, but we mention that a specific example we examined is the traveling salesman problem. This NP-complete optimization problem can be solved very fast by an appropriate single electron network. For details, we refer the reader to [8].

# IV. FABRICATION OF NEUROMORPHIC NETWORKS: SELF-ASSEMBLY

We now address the fabrication of these networks. Conventional nanolithography involving electron beam, ion beam, x-ray or even scanning tip lithography [37] are unsuitable for fabricating single-electron circuits for two basic reasons: 1) they are usually *serial* in nature (direct-write techniques) whereby the patterns on each wafer must be exposed sequentially, resulting in a throughput that is unacceptably slow for commercial mass production; and 2) they often cause significant radiation damage to processed nanostructures [38]–[43]. In contrast, the recently developed techniques for self-assembly of periodic quantum dot arrays [14], [44] suffer from neither of these drawbacks and therefore offer an attractive choice.

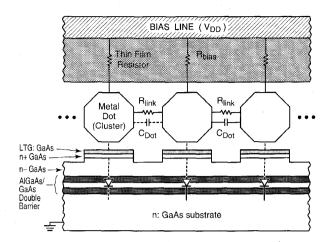

Fabrication of the network shown in Fig. 1(a) has three key elements: 1) deposition of a regimented, *periodic* array of nanosized metallic islands on a RTD; 2) electrical isolation of these islands via mesa-etching through the RTD; and 3)

linking the islands with molecular wires or some other means. Fabrication of a periodic, 2D array of metallic islands with diameters in the 5–100 nm range has been demonstrated by us using electrochemical self-assembly [44]. This approach has two advantages over conventional direct-write lithography (e.g., e-beam, ion-beam or STM lithography). First, it is a "gentle" technique that does not cause serious processing damage, and second, it is *parallel* in nature whereby large batches of wafers can be processed simultaneously and all patterning on a given wafer is performed simultaneously, resulting in several orders of magnitude improvement in throughput. In order to illustrate the feasibility of realizing nanoscale circuits using these methods, we outline a specific process which employs self-assembly techniques, several of which have been developed by the authors and their collaborators.

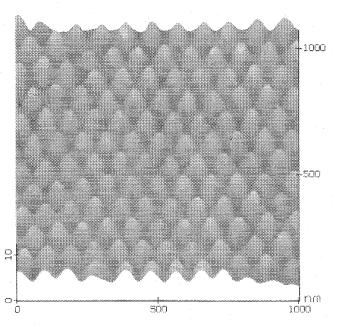

First, using molecular beam epitaxy, an RTD structure is synthesized and capped by a thin (3 nm) low-temperature grown GaAs layer (LTG:GaAs), which is highly resistant to oxidation [45] and which serves to passivate underlaying doped layers [45], [46]. Then on the surface of this layer, a thin-film of Al ( $\sim$ 100-nm-thick) is resistively evaporated. This film is electropolished in perchloric acid/butyl cellusolve/ethanol/distilled water at 60 V for 30 s resulting in a dimpled surface containing a highly periodic array of crests and troughs as shown in the *raw* atomic force micrograph data in Fig. 8.

The trough regions of this dimpled film can be selectively etched away by bromine/methanol leaving isolated islands of Al (the crests) on the surface (see Fig. 9). The trough regions are etched away before the crests since the Al film is much thinner in these regions (by approximately 50 nm). In fact, the ratio of the Al film thicknesses in the crest and trough regions can be easily made as large as 10:1 which facilitates selective etching of the troughs. This results in a 2D periodic array of nano-sized metallic islands on the surface (vestiges of the crests) which now need to be electrically isolated. For this, we

Fig. 8. Atomic force micrograph of a dimpled electropolished Al surface showing a periodic array of crests and troughs. This pattern is self-organized. The height of the crests above the troughs is about 50 nm.

proceed as follows. One can use this periodic array of islands as a mask to shallow-etch electrically isolated mesas capped by the metal Al. The use of the metallic island array as the etching mask for patterning the RTD substrate provides a selfalignment between the metal islands and the semiconductor mesas. Deep etching is not feasible, due to the small areas of the Al dots and the need to keep a relatively planar surface for subsequent interconnect steps. The LTG:GaAs layer allows one to keep the underlying n-GaAs layer very thin without risking oxidation [45]. The isolation etch can be shallow since the removal of the LTG:GaAs layer eliminates the passivation effect, resulting in the depletion of the regions between the islands. The final step is to electrically link the islands. For this, the space between the mesas may be filled up with a chosen material by electrodeposition, sputtering, or lowtemperature grown MBE layer to create a resistive and/or capacitive connection between the dots.

Instead of using the electropolished Al technique, one can also deposit a self-assembled, 2D network of metal clusters on the surface of the substrate with adjacent clusters linked by molecular wires. Techniques to deposit ordered arrays of nanometer diameter Au clusters on various flat substrates, to deposit organic molecules (molecular wires) between adjacent clusters have been demonstrated and the in-plane electronic conduction through arrays of 4 nm clusters deposited between lithographically defined contacts has been studied [14], [15], [47]. Again, the deposited cluster network can be used as a self-aligned mask to etch through the RTD and create mesas capped by metal dots (Fig. 10). The inter-island links are already provided by the molecular wires. Although the technology of molecular wires is in its infancy, significant progress has been made in the synthesis, characterization and modeling of molecular wires suitable for this application [48], [49]. The advantages of molecular wires are: 1) great

flexibility in choosing the resistance and capacitance between clusters [48]; and 2) electrical access to individual nanometer sized dots may be feasible due to the nanometer size scale of the wires and the ability to deposit wires on selective regions based on the composition of the regions and of the molecular end groups. These capabilities would be necessary for realizing certain processors where one needs variable interisland resistances and capacitances as well as image processors where one needs to address individual dots.

The fabrication steps outlined to this point have addressed the metallic island array, the interisland linking and the RTD substrate required for the computational cells. The same techniques used to provide resistive linking between islands can provide the linking between islands at the edge of the array and input/output or programming contacts. In "edge-driven" configurations, the computational cells will also require a resistive link between each island and a bias plane, presumably located above the island array, to provide the current bias required to achieve bistability in voltage. This capability appears feasible using either molecular wires or a thin-film resistive layer deposited between the island array and the bias plane. It should be noted that the most time consuming "directwriting" steps of nanolithography have been replaced by chemical self-assembly in the proposed synthesis techniques. In principle, large batches of wafers can be electropolished and subsequently etched in a large bath, thereby making the electropolishing technique a truly parallel process with fast throughput. The self-assembly synthesis of metallic cluster arrays could also be a high throughput process. This is a significant advantage over "direct" write based fabrication processes for nanoscale circuits.

The ability to realize individual address lines for each island, while beyond the capability of the self-assembly techniques presented here, would allow configurations where individual

Fig. 9. Fabrication steps to realize the neuromorphic network in Fig. 1(a) using self-assembly techniques. The steps are described in the text. The inter-island connection is made *not* by molecular wires, but by an electrode-posited, sputtered or MBE-grown layer grown on the etched surface. A wide variety of layer materials can be used, resulting in phase-coherent, rectifying, resistive or capacitive links.

islands could be addressed in order to provide input/output or programming, Achieving this type of interconnect configuration at the nanometer scale would require significant advances in technology, but may be possible using scanning probe based lithography.

In order to establish the feasibility of the proposed synthesis techniques, it is informative to consider the ranges of capacitance and resistances achievable with these techniques. Using a conservative estimate for the minimum achievable island diameter of 20 nm, the capacitances between adjacent islands and between an island and the substrate will be on the order of 10<sup>-18</sup> F, corresponding to Coulomb charging energies of about 70 meV. Molecular wires which have been reported to date have resistances on the order of 20–40 M  $\Omega$  per molecule when bridged between metal electrodes [15], [48], [49]. Since metallic clusters with 20-nm diameters can have hundreds of molecular wires in parallel between each pair of adjacent clusters, achievable island to island resistances should be on the order of 0.1–10 M  $\Omega$  [15], [47], [49]. In order to bridge distances significantly longer than 2 nm, networks of these molecular wires may be required. An RTD substrate with peak current density of  $1 \times 10^5$  A/cm<sup>2</sup> would yield a peak current of 0.3  $\mu$ A for each semiconductor mesa, assuming that the current density remained constant as device dimensions

Fig. 10. Another possible fabrication strategy where the metal dots are clusters self-assembled on the surface and linked by molecular wires.  $R_{\rm link}$  and  $C_{\rm Dot}$  are the interdot resistances and capacitances that are realized by molecular wires. Self-assembly techniques for 2D linked arrays have been demonstrated and the in-plane electronic conduction through such an arrays has been studied (see [14] and [48]).

are scaled down. For a voltage at peak current of 0.5 V, this corresponds to an average resistance of approximately 1.5 M  $\Omega$ for the RTD characteristic. The use of short-chain molecular wires along with a low-resistance, nonalloyed contact structure [50] should provide an interface coupling resistance of less than 200 K  $\Omega$  between the metal island and the semiconductor mesa for this island size. The devices can be effectively current biased if the resistance from a bias plane, located above the array, to each island is much greater than the characteristic resistance of the RTD mesa. Since the resistance through certain molecular wires consists of state-assisted tunneling [48], a suitable resistance, e.g., a resistance on the order of 5–10 M  $\Omega$ , could be achieved by using longer molecular wires to connect each island to the bias plane. It may also be possible to use a thin-film resistive material deposited between the metallic island array and the bias plane to realize the linking of each island both to adjacent islands and to the bias plane. A resistivity of approximately 50  $\Omega$  · cm would be required; an ideal material would also possess an anisotropic resistivity characteristic to allow independent control of the vertical and horizontal linking resistances. It therefore appears feasible to realize appropriate resistance and capacitance elements for the proposed computational cells using the technologies discussed in this section.

#### V. CONCLUSION

In conclusion, we have presented a neuromorphic architecture for powerful computing and signal processing applications using an array of metallic islands on a resonant tunneling diode. Some of the components required to fabricate these circuits are in their infancy. Nontheless, the rapid progress in nanoelectronics may make these circuits a reality in not too distant a future.

### ACKNOWLEDGMENT

The authors are indebted to numerous colleagues for insightful discussions. We are especially grateful to Dr. J. A. Cooper,

Jr., Dr. P. Balasingam, Dr. M. Cahay, Dr. A. E. Miller, Dr. R. P. Andres, Dr. J. M. Woodall, and Dr. R. Landauer.

#### REFERENCES

- [1] R. T. Bate, G. A. Frazier, W. R. Frensley, J. W. Lee, and M. A. Reed, Proc. SPIE, vol. 792, pp. 26-35, 1987; R. T. Bate, Solid State Technol., vol. 32, p. 101, 1989.

- [2] P. Bakshi, D. Broido, and K. Kempa, J. Appl. Phys., vol. 70, p. 5150,

- [3] H. Korner and G. Mahler, Phys. Rev. B, vol. 48, p. 2335, 1993; K. Obermayer, W. G. Teich and G. Mahler, Phys. Rev. B., vol. 37, 1987, 8096; W. G. Teich and G. Mahler, Phys. Rev. A., vol. 45, p. 3300, 1992.

[4] S. Lloyd, Science, vol. 261, p. 1569, 1993; S. Lloyd, Science, vol. 263, p. 695, 1994.

[5] C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernstein, Nanotech-

nology, vol. 4, p. 49, 1993.

[6] S. Bandyopadhyay, B. Das, and A. E. Miller, Nanotechnology, vol. 5, p. 113, 1994.

[7] A. N. Korotkov, Appl. Phys. Lett., 67, 2412 1995.

[8] P. Balasingam and V. P. Roychowdhury, "nanoelectronic Functional Devices," School of Electrical Engineering, Purdue Univ., West Lafayette,

IN, Tech. Rep. TR-EE 94-24, 1994. S. Bandyopadhyay and V. P. Roychowdhury, *IEEE Potentials*, p. 8, Apr.-May 1996; S. Bandyopadhyay and V. P. Roychowdhury, *Jpn. J.* Appl. Phys., pt. 1, vol. 35, p. 3350, 1996; V. P. Roychowdhury, X. Wang, and S. Bandyopadhyay, in presented at 8th Int. Conf. Superlattices, Microstructures, and Microdevices, Cincinnati, OH, Aug. 24, 1995.

[10] R. A. Kiehl and T. Ohshima, in Extended Abstracts of the International Conference on Solid State Devices and Materials, SSDM'95, Osaka,

Japan, p. 210. To appear in Jpn. J. Appl. Phys.

[11] R. Landauer, keynote talk given at the Workshop on Physics and Computation, PhysComp '92, Dallas, TX, Oct. 2-4, 1992, (available as an IEEE Computer Society Press Reprint); R. Landauer, in "Ultimate Limits of Fabrication and Measurement", (NATO-ASI Series), M. E. Welland, ed. Dordrecht: Kluwer, 1994.

\_, IBM J. Res. Develop., vol. 5, p. 183, 1961.

- [13] R. Tsu and L. Esaki, *Appl. Phys. Lett.*, vol. 22, p. 562, 1973.

[14] R. G. Osifchin, R. P. Andres, J. I. Henderson, and C. P. Kubiak, to be published; R. G. Osifchin, W. Mahoney, R. P. Andres, J. I. Henderson, C. P. Kubiak, and R. N. Dominey, Superlattices and Microstructures

- vol. 18, pp. 283–289, 1995. [15] D. B. Janes, V. Kolagunta, R. G. Osifchin, and R. P. Andres, "Electronic conduction through two-dimensional arrays of nanometer diameter metal clusters," Superlattices and Microstructures, vol. 18, pp. 275-282, 1995.

- G. M. Whiteside, Sci. Amer., p. 146, Sept. 1995.

D. S. Bethune, R. D. Johnson, J. R. Salem, M. S. deVries, and C. S. Yannoni, Nature, vol. 366, p. 123, 1993; N. Sudhakar, S. V. Sharma, L. S. Grogoryan, P. Chand, A. K. Majumdar, P. K. Dutta, S. B. Samanta, and A. V. Narlikar, Phys. Lett. A, vol. 170, p. 235, 1992.

- [18] V. Bogomolov, Y. Kumzerov and S. Romanov, Physics of Nanostructures, J. H. Davies and A. R. Long, Eds. Edinburgh, UK: Scottish Universities Summer School in Physics Publications, 1992, p. 317.

- [19] G. Binnig, H. Rohrer, C. Gerber, and E. Weibel, Appl. Phys. Lett., vol. 40, p. 178, 1982; G. Binnig, H. Rohrer, C. Gerber, and E. Weibel, Phys. Rev. Lett., 49, p. 57, 1982.

- [20] M. I. Lutwwyche and Y. Wada, J. Vac. Sci. Technol. B, vol. 13, p. 2819, 1995.

- [21] E. J. P. Santos and M. C. McDonald, J. Vac. Sci. Technol. B, vol. 11, 2362, 1993,

- [22] G. Nicolis and I. Prigogine, Exploring Complexity. New York: Freeman, 1989.

- J. J. Hopfield, in Proc. Natl. Acad. Sci., vol. 79, p. 2554, 1982; J. J. Hopfield and D. W. Tank, Science, vol. 233, 625, 1986.

- [24] S. Grossberg, Neural Networks, vol. 1, p. 17, 1988.

[25] M. A. Cohen and S. Grossberg, IEEE Trans. Syst. Man, Cybern., vol. SMC-13, p. 815, 1983.

- [26] A. N. Michel, J. A. Farrel, and W. Porod, IEEE Trans. Circuits Syst., vol. 36, p. 229, 1989.

- [27] H. J. Levy, D. A. Collins, and T. C. McGill, in Proc, IEEE Int. Symp. Circuits and Syst., New York, 1992; also in Tech. Dig. ISCAS. New York: IEEE Press

- T. E. Stern, Theory of Non-linear Networks and Systems. Reading, MA: Addison-Wesley, 1965.

- A. N. Wilson, Non-linear Networks: Theory and Analysis. New York: IEEE Press 1974

- [30] B. J. van Wees, et al., Phys. Rev. Lett., vol. 60, p. 848, 1988; D. A. Wharam, et al., J. Phys. C., vol. 21, p. L209, 1988.

- [31] M. Amman, R. Wilkins, E. Ben-Jacob, P. D. Maker, and R. C. Jaklevic, Phys. Rev. B, vol. 43, p. 1146, 1991.

- S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1981.

- [33] A. A. Andronov, A. A. Vitt, and S. E. Khaikin, Theory of Oscillators. New York: Dover, 1966.

- [34] D. W. Jordan and P. Smith, Non-linear Ordinary Differential Equations. Oxford, UK: Clarendon, 1987.

- [35] N. S. Bakhvalov, G. S. Kazachca, K. K. Likharev, and S. I. Serdyukova, Sov. Phys. JETP, vol. 68, p. 581, 1989.

- U. Geigenmüller and G. Schön, Europhys. Lett., vol. 10, p. 765, 1989.

- [37] E. E. Ehrichs, R. M. Silver, and A. L. deLozanne, J. Vac. Sci. Technol. A, vol. 6, p. 540, 1988.

- [38] B. Das, S. Subramaniam, and M. R. Melloch, Semicond. Sci. Technol.,

- vol. 8, p. 1347, 1993. [39] D. C. Tsui, A. C. Gossard, and G. J. Dolan, *Appl. Phys. Lett.*, vol. 42,

- p. 180, 1983. T. Fink, D. D. Smith, and W. D. Braddock, *IEEE Trans. Electron* Devices, vol. 37, p. 1422, 1990.

- T. B. Stellwag, M. R. Melloch, J. A. Cooper, Jr., S. T. Sheppard, and D. D. Nolte, J. Appl. Phys., vol. 71, p. 4509, 1992.

- C. M. Knoedler, J. Appl. Phys., vol. 68, p. 1129, 1990.

[43] M. R. Melloch, private communication.

- A. E. Miller, S. Bandyopadhyay, G. Banerjee, D-F Yue, and M. Chandrasekhar, unpublished, 1995; S. Bandyopadhyay, A. E. Miller, and M. Chandrasekhar, in Proc. of SPIE, Photonics West'95, San Jose, CA, (PAGE NOS?) Feb., 1995

- [45] E. H. Chen, D. McInturff, T. P. Chin, M. R. Melloch, and J.M. Woodall, Appl. Phys Lett., vol. 68, p. 1678, 1996.; S. Hong, D. B. Janes, D. McInturff, R. Reifenberger, and J. M. Woodall, "Stability of a lowtemperature grown GaAs surface layer following air exposure using

- tunneling microscopy," to be published.

D. C. Look, D. C. Walters, C. E. Stutz, K. R. Evans, and J. R. Sizelove, "Mechanisms for GaAs surface passivation by a molecular beam epitaxial cap layer grown at 200 C," J. Appl. Phys., vol. 12, pp. 5981-5984, 1992.

- R. P. Andres, J. D. Bielefeld, J. I. Henderson, D. B. Janes, V. R. Kolagunta, C. P. Kubiak, W. J. Mahoney, and R. G. Osifchin, "Synthesis and electrical characterization of a two-dimensional superlattice of molecularly linked metal clusters," to appear in Science.

- [48] M. P. Samanta, W. Tian, S. Datta, J. I. Henderson, and C. P. Kubiak, "Electronic conduction through organic molecules," *Phys. Rev. B*, vol. 53, p. 7626R, 1996; W. Tian, M. P. Samanta, and S. Datta, to be published.

- [49] R. P. Andres, T. Bein, M. Dorogi, S. Feng, J. I. Henderson, C. P. Kubiak, W. Mahoney, R. G. Osifchin, and R. G. Reifenberger, ' staircase' single electron tunneling at room temperature in a selfassembled molecular nanostructure," Science., vol. 272, pp. 1323-1324, 1996

- M. P. Patkar, T. P. Chin, J. M. Woodall, M. S. Lundstrom and M. R. Melloch, "Very low resistance nonalloyed ohmic contacts using lowtemperature molecular beam epitaxy of GaAs," Appl. Phys. Lett., vol. 66, pp. 1412-1414, 1995.

Vwani P. Roychowdhury (M'89) received the B.Tech. degree from the Indian Institute of Technology, Kanpur, and the Ph.D. degree from Stanford University, Stanford, CA, in 1982 and 1989, respectively, both in electrical engineering.

From September 1989 to August 1991, he was a Research Associate, Department of Electrical Engineering, Stanford University. Currently, he is an Associate Professor, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN. His research interests include

parallel algorithms and architectures, design and analysis of neural networks, application of computational principles to nanoelectronics, special purpose computing arrays, VLSI design and fault-tolerant computation. He has coauthored several books including Discrete Neural Computation: A Theoretical Foundation (Prentice Hall, 1995) and Theoretical Advances in Neural Computation and Learning (Kluwer, 1994).

Dr. Rovchowdhury was named the General Motors Faculty Fellow in the School of Engineering at Purdue University from 1992 to 1994. For his outstanding performance in the classroom, he received the 1993 Ruth and Joel Spira Outstanding Teacher Award.

David B. Janes (S'86–M'89) was born in Somerset, KY, in 1958. He received the B.A. degree in physics (summa cum laude) from Augustana College, Rock Island, IL, in 1980, and the B.S.E.E. (highest honors), M.S.E.E., and Ph.D. degrees from the University of Illinois, Urbana-Champaign, in 1980, 1981, and 1989, respectively. His doctoral research focused on the effect of deep levels on the performance of acoustic charge transport devices.

From 1981 to 1985, he was a Research Scientist in the Research Division, Raytheon Company, where he was involved in research on microwave semiconductor devices, including GaAs IMPATT diodes and MESFET's, and monolithic microwave integrated circuits. Since 1989, he has been an Assistant Professor, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN. He is presently engaged in experimental research on mesoscopic semiconductor devices and metallic cluster arrays, characterization of novel semiconductor heterostructures, and microwave devices based on compound semiconductor heterostructures.

Supriyo Bandyopadhyay (SM'89) received the B. Tech. degree from the Indian Institute of Technology, Kharagpur, in electronics and electrical communications engineering in 1980, the M.S. degree in electrical engineering from Southern Illinois University, Edwardsville, in 1982, and the Ph.D. degree in electrical engineering from Purdue University, West Layfayette, IN, in 1985.

Currently, he is an Associate Professor, Department of Electrical Engineering, University of Notre Dame, South Bend, IN. He has authored about 150

articles in his various fields of interest which include quantum devices, hot electron transport, superlattice physics, nonlinear optics, and superconductivity. He has chaired many international conferences and edited books in these fields.

Dr. Bandyopadhyay is a member of Tau Beta Pi, Eta Kappa Nu, Sigma Pi Sigma, and the American Physical Society. He is also listed in Who's Who in Science and Technology, the Dictionary of International Biography, (Cambridge, UK), and Sterling's Who's Who.

Xiaodong Wang received the B.S. degree in electrical engineering from Shanghai Jiao Tong University, Shanghai, China, in 1992, and the M.S. degree in electrical engineering from Purdue University, West Lafayette, IN, in 1995. He is currently a Ph.D student in the Department of Electrical Engineering, Princeton University, Princeton, NJ. He has worked in the areas of digital communications, and parallel and distributed computing.