## FPGA Temperature Dependent Leakage Modeling Week 2 Progress Report 1/21/05 Wong, Ho-Yan Phoebe

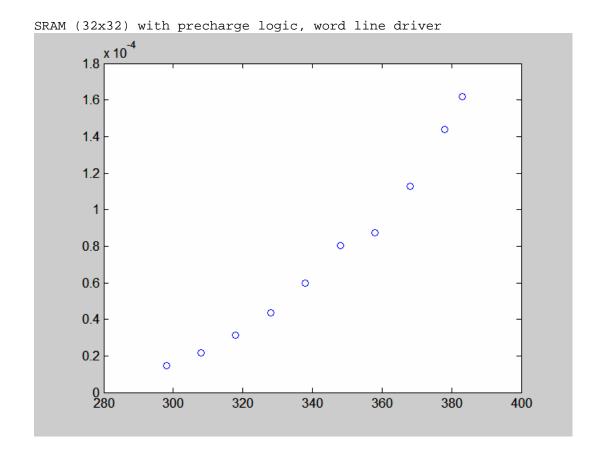

- 1. SRAM and LUT leakage did not demonstrate a monotonic behavior with temperature. After different trials, it was found that if the SRAM word line voltage is set to a higher value, the problem disappears. So for now, the simulation setting is Vdd=1V, Vt=0.2V, Vt\_SRAM=0.65V, and V\_word line is 1.35V.

- 2. The above device setting is verified to be valid by testing the read and write operation in SRAM.

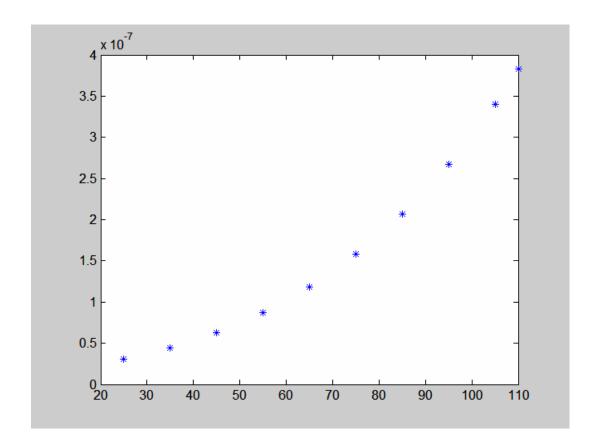

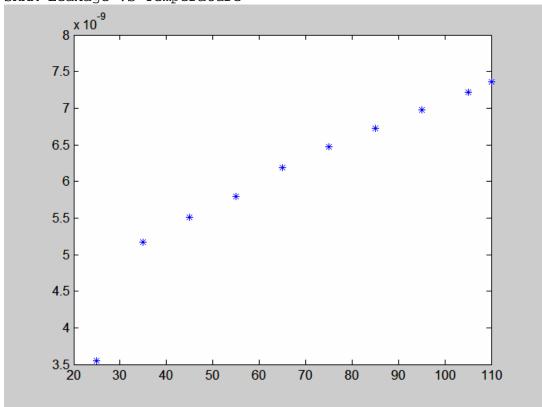

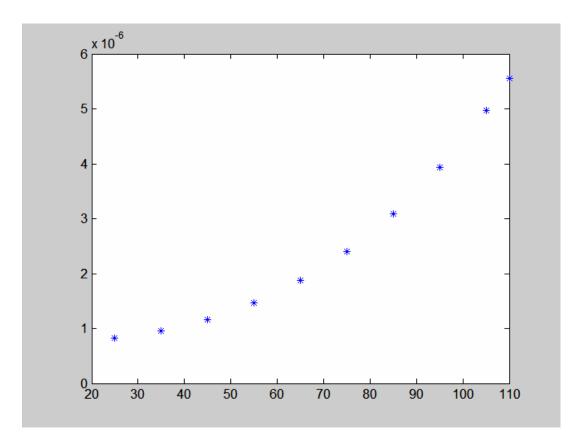

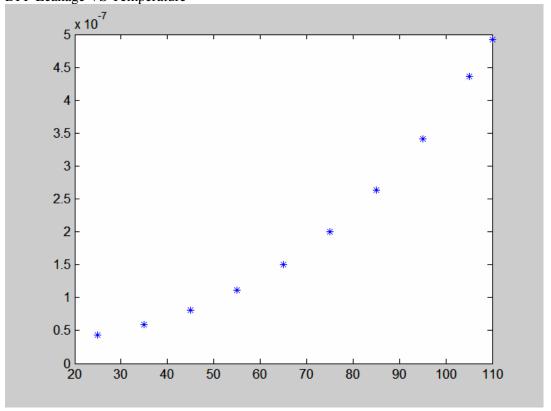

- 3. All the leakage current components required by the power simulator are simulated using HSPICE. The curves are as follows. Curve fitting will be done as the next step.

SRAM Leakage VS Temperature

LUT4 Leakage VS Temperature

DFF Leakage VS Temperature

Buffer 4x Leakage VS Temperature