## Signal Integrity

Lecture 22 Alessandra Nardi

### Introduction

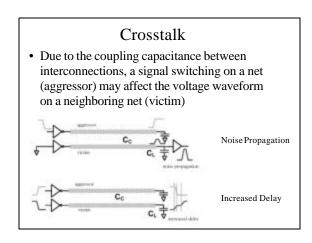

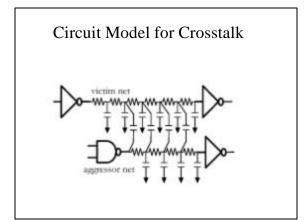

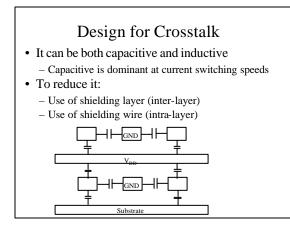

• Signal Integrity includes all IC design effects that cause the design to malfunction due to the distortion of the signal waveform:

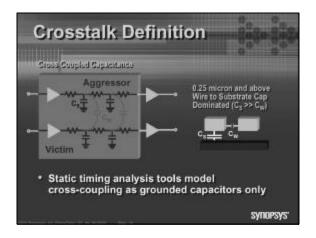

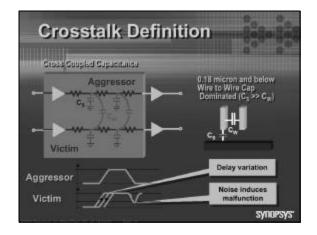

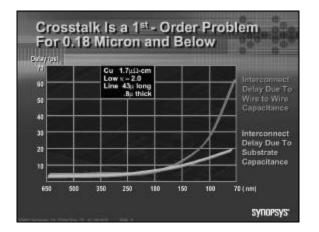

- Crosstalk (for delay and noise)

- Power/Ground (P/G) integrity

- IR-drop

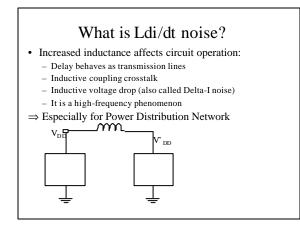

- Ldi/dt noise

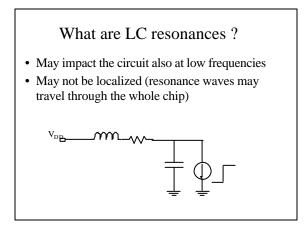

- LC resonances

- Substrate coupling

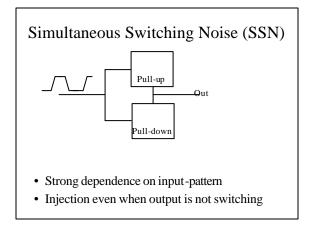

- Simultaneous switching noise

## P/G Integrity

- Technology scaling imposes requirements on the reduction of power supply voltage

- Power/Ground integrity becomes a serious challenge during design

- 10% supply voltage fluctuations may translate in more than 10% timing inaccuracy

- Or even cause circuit to fail

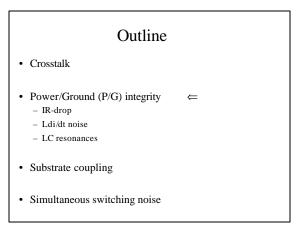

### Outline

- Crosstalk

- Power/Ground (P/G) integrity

- IR-drop Ü

- Ldi/dt noise

- LC resonances

- · Substrate coupling

- Simultaneous switching noise

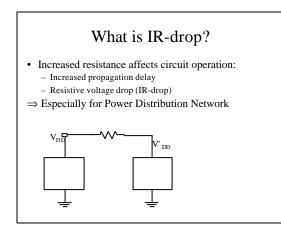

### **IR-drop consequences**

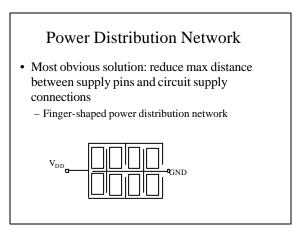

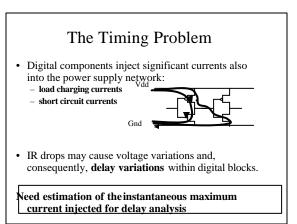

- · Design and layout of power distribution network must be done early in the design process (then gradually refined)

- Design of the power network requires knoledge of the peak current (as opposed to power dissipation that relates to average current)  $\Rightarrow$  Reliability

- · Delay is increased

- · Noise Margins are reduced

- Technology scaling worsen the problem

- IR-drop - Ldi/dt noise

· Crosstalk

- LC resonances Ü

- Substrate coupling

- · Simultaneous switching noise

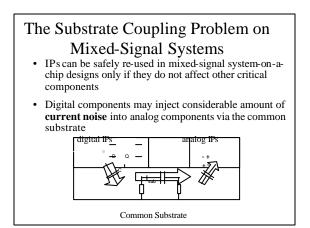

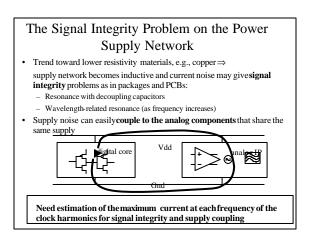

# The Substrate Coupling Mechanisms: Need for Current Spectrum Estimation Why substrate currents? Substrate potentials may affect analog signals: though direct capacitive coupling through variation of Vt (body effect) Digital IPs inject current noise into the substrate at clock frequency and its harmonics because of switching activity Substrate potentials Why frequency domain? Analog circuits are particularly sensitive in their frequency band

Analog circuits are particularly sensitive in their frequency band of operation

Need estimation of the maximum current injected by digital components for each harmonic of their clocks

for safe operation!

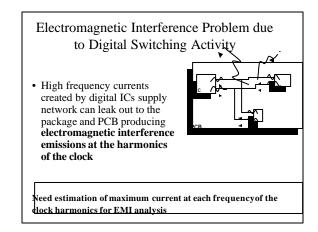

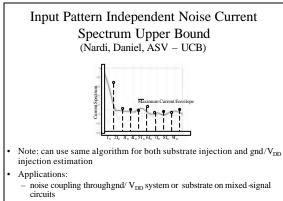

# Estimation Techniques PROBLEMS REQUIREMENTS • Substrate coupling max substrate current at each harmonic • Timing max supply current instantaneous in time • Power consumption average supply current over many periods in time • Supply coupling max supply current at each harmonic

- EMI

- max supply current at each harmonic

### Vast literature on supply current estimation for power consumption: mainly concerned with average current in time [Najim TransVLSI94] Most are based on switching activity estimation with propagation of probability distributions

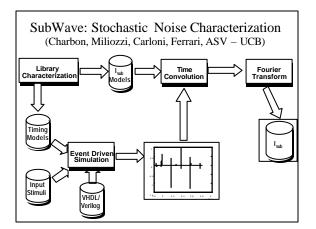

Some Approaches for Noise Current Estimation

- Some algorithms exist for maximum current envelope estimation instantaneously in time [Bobba ISPD98]. Mainly fortiming problems, not suitable for substrate coupling, signal integrity and EMI.

- Stochastic approach for current estimation in the frequency domain

[Demir ICCAD99]: combines the approach from power analysis based on propagation of switching activity probabilities, with an estimation of frequency spectrum for substrate or signal integrity problems

- [Charbon TransCAD99]

- Missing an approach for current upper bound estimation in the frequency domain

- Electromagnetic interference

## Summary on Signal Integrity

- Crosstalk

- Power/Ground (P/G) integrity

- IR-drop

- Ldi/dt noise

- LC resonances

- Substrate coupling

- Simultaneous switching noise