### Effects of On-chip Inductance on Power Distribution Grid

Atsushi Muramatsu Dept. Communications & Computer Engineering **Kyoto University**

u.ac.ip

Masanori Hashimoto Dept. Information Systems Engineering Osaka University

muramatsu@vlsi.kuee.kyoto- hasimoto@ist.osakau.ac.jp

Hidetoshi Onodera Dept. Communications & Computer Engineering Kyoto University

onodera@i.kyoto-u.ac.jp

#### **ABSTRACT**

With increase of clock frequency, on-chip wire inductance starts to play an important role in power/ground distribution analysis, although it has not been considered so far. We perform a case study work that evaluates relation between decoupling capacitance position and noise suppression effect, and we reveal that placing decoupling capacitance close to current load is necessary for noise reduction. We experimentally show that impact of on-chip inductance becomes small when on-chip decoupling capacitance is well placed according to local power consumption. We also examine influences of grid pitch, wire area, and spacing between paired power and ground wires on power supply noise. Minification of grid pitch is more efficient than increase in wire area, and small spacing reduces power noise as we expected.

### **Categories and Subject Descriptors**

B.7.2 [Integrated Circuits]: Design Aids.; B.8.2 [Performance and Reliability]: Performance Analysis and Design Aids.

### **General Terms**

Performance, Design.

### **Keywords**

power distribution network, on-chip inductance, power supply noise, decoupling capacitance

### INTRODUCTION

On-chip power/ground network analysis currently considers inductances of package and bonding wires commonly. On the other hand, inductances of on-chip wires are hardly considered, because inductances of on-chip wires are smaller than those of package and bonding wires so far. In addition, in low clock frequency, impedance due to resistance is dominant. However, packages with low parasitic inductance, such as a flip-chip package, are becoming popular. As clock frequency increases, power supply noise contains higher frequency components, and reactance  $\omega L$  dominates

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

ISPD'05, April 3–6, 2005, San Francisco, California, USA. Copyright 2005 ACM 1-59593-021-3/05/0004 ...\$5.00.

impedance of the power network instead of resistance. In the future, power/ground analysis for high-speed circuits needs to consider on-chip inductance.

Reference [1] gives an outline of LSI power distribution system with on-chip wire inductance and estimation of on-chip inductance in power grid. Reference [1] also shows that on-chip power grid behaves as a 2D transmission line, and noise propagates as a wave. Reference [2] proposes a fast simulation method for power grid based on transmission theory. Reference [3] discusses optimal wire structures of on-chip power/ground lines from the point of on-chip inductance. Reference [4] is a prior work that presents power distribution analysis without considering on-chip wire inductance underestimates voltage fluctuation by over 50%. Reference [4] also indicates that the effect of on-chip inductance becomes significant when package impedance is small. Although these works start to study power network analysis with on-chip wire inductance, it is still unclear in what conditions we must consider on-chip inductance. This paper discusses behaviors of power/ground network with on-chip inductance, and evaluates analysis error due to ignoring on-chip inductance. From our experiments focusing on distribution of power consumption and policy of decoupling capacitance insertion, we reveal conditions that on-chip inductance must be considered, and demonstrate that position of decoupling capacitance is important to mitigate on-chip inductance effect as well as to reduce power supply noise. We also study how we should design robust power distribution network in point of grid pitch, power/ground wire area, and spacing between paired power and ground wires.

Section 2 gives a description of an equivalent circuit used in LSI power/ground network analysis. Section 3 discusses response of power distribution network excited by one current source. Section 4 shows simulation results when power consumption is not uniform, and discusses relationship among on-chip inductance, power consumption distribution and decoupling capacitance positions. Section 5 examines the relation between physical parameters of power grid and voltage fluctuation. Finally, conclusion is remarked in Section 6.

### EQUIVALENT CIRCUIT MODEL FOR **POWER GRID ANALYSIS**

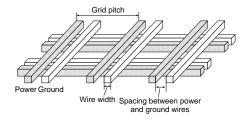

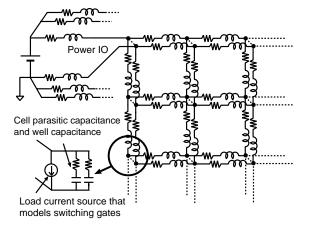

Power distribution network in LSI is usually analyzed by using simplified equivalent circuit models since it is very complex and large. Figure 1 shows the power grid structure we analyze in this paper. Power wires and ground wires run in parallel in the same layer. In this paper, we consider the topmost power grid only. Figure 2 is an example of a popular equivalent circuit [5]. Onchip power/ground wires are modeled in lumped resistance, self-

Figure 1: Power grid structure.

Figure 2: A simple model of LSI power distribution circuits.

inductance, mutual inductance, and capacitance. Junction capacitance and gate capacitance inside logic gates are connected between power and ground lines through on-resistance of MOS transistors. Well junction capacitance is also connected. Load current that working circuits consume is modeled in a current source. When we model silicon substrate, resistance mesh is connected to ground lines, although Fig. 2 does not include the substrate model. Power IOs, which supply current from PCB to LSI, are often modeled in series of an inductance and a resistance. This circuit corresponds to parasitic elements of bonding wire and package line. We often connect ideal voltage sources outside the package when we analyze on-chip power distribution network.

On-chip inductance is traditionally ignored, because on-chip inductance is smaller than package inductance and analyzing power network with on-chip inductance requires huge computational cost. However, flip-chip package using bump-arrayed power IO reduces parasitic inductance to below 1nH. Thus, on-chip inductance is now comparable with package inductance. On-chip inductance depends on wire structure, especially length. When paired P/G wires with  $10\mu$ m width are routed with  $100\mu$ m pitch, the self-inductance is hundreds pH/mm. Another reason that makes the effect of on-chip inductance significant is improvement in circuit operation speed. In high frequency operation, reactance in power/ground lines becomes comparable with, or larger than resistance, and hence it has a significant impact on power delivery system.

Simulating a circuit with on-chip inductance expends much time than without on-chip inductance. Hence, some simplifications of circuits that have many inductances are proposed (survey is found in Ref. [6]). These methods reduce simulation time. There is, however, a problem that simplification may spoil accuracy and/or convergence. Therefore in this paper, we do not truncate any partial

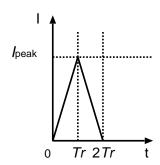

Figure 3: Waveform of load current.

mutual inductances to accurately evaluate impact of on-chip inductance in Section 3 and 4. On the other hand, in Section 5, we use a simplification technique to analyze finer power grid.

### 3. DEPENDENCY OF VOLTAGE FLUCTU-ATION ON SLOPE OF LOAD CURRENT AND DECAP POSITION

Section 2 describes an equivalent circuit model of LSI power network. In this model, superposition theory holds, since it is a linear circuit. The overall voltage fluctuation can be computed by superposing every voltage fluctuation caused by each current source. This section discusses behaviors of power distribution circuits with a single current source in order to clearly evaluate impact of onchip inductance on power voltage fluctuation.

### 3.1 Current slope vs. noise amplitude

We first study a dependency of power supply fluctuation on current slope (di/dt). We vary transition time of load current  $T_r$  in Figure 3 and evaluate the power supply noise assuming a  $0.13\mu m$ technology. The power grid network used in the experiment is as follows. The chip size is  $2 \times 2 \text{mm}^2$ . Wire material is aluminium. Power grid is routed with  $100\mu m$  pitch. The wire width and thickness are  $10\mu m$  and  $1\mu m$  respectively. Ground wires are routed similarly. We calculate partial self inductance and partial mutual inductance between parallel lines using an analytic approach based on Geo-Metrical Distance (GMD) concept [7]. We then construct a full PEEC model [8], which means all mutual inductances are included. Partial self-inductance of power line is 585pH/mm. Power source is 1.2V. We attach nine paired power/ground IO-cells whose inductance and resistance are 0.5nH and  $1\Omega$ . We assume that logic (NAND) gates occupy half of chip area, and the capacitance that those gates have is connected between power and ground lines. Silicon substrate is not considered in our analysis. A load current source is placed at center of the chip. The current is decided such that all NAND gates placed in  $3000\mu m^2$  area switch. The transition time Tr of the current is set to 50, 66, 100ps. When Tr = 50ps, the peak current is 32.8mA.

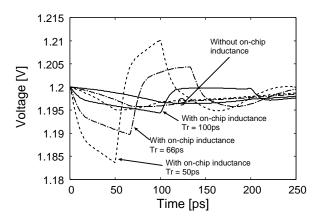

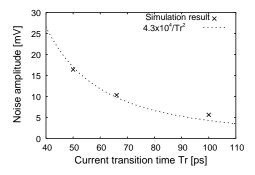

Figure 4 shows the simulation results with and without on-chip inductance. Without on-chip inductance, the voltage fluctuations are almost the same even though Tr varies. On the other hand, Figure 5 shows that the voltage fluctuation with on-chip inductance changes and the peak values are 5.6mV, 10.3mV, and 16.4mV, which are almost in inverse proportion to  $Tr^2$ . In this situation, a small portion of the circuit consumes power, and a lot of capacitance that works as decoupling capacitance is available on the chip. However there is not enough decoupling capacitance close to the

Figure 4: Voltage fluctuation with and without on-chip inductance in various Tr conditions.

Figure 5: Dependency of voltage fluctuation on transition time  $T_r$ .

current source, which causes excessively large voltage fluctuation due to on-chip inductance.

## 3.2 Relationship among decap size, decap position and noise amplitude

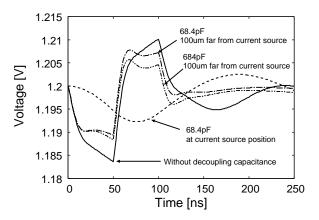

We next attach a decoupling capacitance to power grid, and evaluate effect of suppressing voltage fluctuation by circuit simulation. Results are shown in Fig. 6. We place a decoupling capacitor at two different positions; at the same place with the load current source, and the place  $100\mu m$  away from the load current source. The capacitance value is 68.4pF, and it is large enough to suppress voltage fluctuation when it is placed at the same place with the load current source. The capacitance of 68.4pF corresponds to MOS gate area of  $5{,}000\mu\text{m}^2$ . When the decoupling capacitance is placed at the load current source, the voltage fluctuation is substantially reduced. On the other hand, the capacitance placed  $100\mu m$  away from the current source can not suppress the voltage fluctuation effectively. Even if we increase the capacitance value to 684pF, which is impossible to integrate in a grid, voltage fluctuation is not suppressed as long as the capacitor is placed  $100\mu m$  away from the current source.

## 3.3 Qualitative analysis of dependency on current slope and decap position

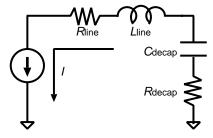

We here analyze the simulation results in the previous subsections qualitatively. The effect of on-chip decoupling capacitance depends on inductance of power/ground lines as well as parasitic series resistance of the decoupling capacitance and resistance of

Figure 6: The effect of decoupling capacitance away from load current (  $Tr=50\,\mathrm{ps}$  ).

power/ground lines between load source and decoupling capacitor. Figure 7 is a very simple equivalent circuit model of local power distribution network that includes a decoupling capacitor and a current source. We here focus on local mechanism of charge supply and use the equivalent circuit in Figure 7, although it can not represents the behaviour of the entire power grid network. Impedance that excludes the capacitance,  $Z_{\rm eff}$ , is expressed by the line resistance and the inductance between the current source and the capacitor ( $R_{\rm line}$ ,  $L_{\rm line}$ ) and the series resistance of the decoupling capacitance ( $R_{\rm decap}$ ). When the load current is triangle as shown in Fig. 7, the impedance  $Z_{\rm eff}$  becomes

$$\frac{dI}{dt} = \frac{I_{\text{peak}}}{Tr} \tag{1}$$

$$Z_{\text{eff}} = \frac{L_{\text{line}} \cdot dI/dt}{I_{\text{peak}}} + R_{\text{line}} + R_{\text{decap}}$$

$$= \frac{L_{\text{line}}}{Tr} + R_{\text{line}} + R_{\text{decap}}, \tag{2}$$

is the transition time of the lead current, and  $I_{\text{cons}}$  is the

where Tr is the transition time of the load current, and  $I_{\rm peak}$  is the peak current. If the decoupling capacitor is so large that the voltage across the capacitance is constant, the maximum drop voltage  $V_{\rm drop}$  is expressed as follows.

$$V_{\text{drop}} = I_{\text{peak}} Z_{\text{eff}}$$

$$= L_{\text{line}} \frac{I_{\text{peak}}}{Tr} + (R_{\text{line}} + R_{\text{decap}}) I_{\text{peak}}. \quad (3)$$

On-chip inductance adds the first term to the voltage drop. This term includes transition time Tr, and hence the voltage drop  $V_{\rm drop}$  depends on not only  $I_{\rm p\,eak}$  but also Tr.

Resistance  $R_{\rm line}$  and inductance  $L_{\rm line}$  are in proportion to the distance between the current source and the capacitor. Therefore, the effect of decoupling capacitance becomes smaller as the distance increases, which is shown in Figure 6. In other words, when on-chip inductance is taken into account and switching speed becomes faster, we must place decoupling capacitance at a closer place to current source.

When the number and the size of switching transistors are unchanged, which means that average power dissipation is the same and is the same situation in Figure 5, the product of  $I_{\rm peak}$  and Tr is constant.  $I_{\rm peak}$  is inversely proportional to Tr. When Tr becomes smaller, the voltage drop due to resistance is in proportion to Tr, and the voltage drop due to inductance is proportional to  $Tr^2$ . This analysis is consistent with the result shown in Figure 5.

Figure 7: An equivalent circuit of power line and decoupling capacitor.

# 4. POWER GRID ANALYSIS FOCUSING DISTRIBUTION OF POWER CONSUMPTION

The previous section shows behaviors of power distribution circuits with a single current source. In actual chips, many load current sources work simultaneously. This section focuses on distribution of power dissipation, and evaluates supply voltage fluctuation. We vary circuit conditions such as switching activity of each circuit block, size and position of decoupling capacitors, and examine impact of on-chip inductance in each condition.

We use a chip model in a  $0.13\mu m$  technology that is similar with that used in Section 3. Power distribution topology is power grid. The pitch of power wires is  $300\mu m$ . The wire width and thickness is  $30\mu m$  and  $1\mu m$ . Ground wires are routed similarly. The power grid size is  $20\times20$ , and the chip size is  $6\times6mm^2$ . We calculate on-chip inductance like Section 3, and then construct a full PEEC model. The supply voltage is 1.2V. The power is supplied through 100 pairs of power IOs. Each power IO has 0.5nH and  $1\Omega$ . We assume that logic gates occupy half of the chip area, and their capacitance is connected between power and ground lines.

Load current sources, in which working circuits are modeled, are placed at each junction of the grid. The clock frequency is 500 MHz. We assume that load current flows at both rising and falling edges of the clock signal, and thereby the cycle of load current is 1 GHz. The transition time Tr of current sources is 50 ps. We simulate this chip with the following two conditions of switching activity; 1) uniform power consumption, i.e. power dissipation at each grid is the same (uniform case), and 2) the power consumption per grid at the center of the chip is five times larger than that at the periphery of the chip (unbalance case). The uniform case assumes that 20% of transistors are switching at the center as well, also 10% of transistors are switching at the periphery. In both cases, the peak current in the whole chip is 590 mA.

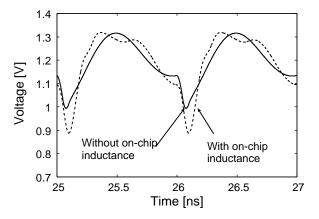

### 4.1 Without decoupling capacitance

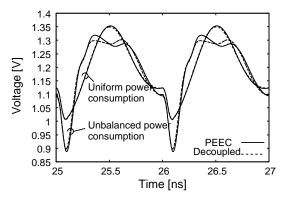

Impact of on-chip inductance depends on distribution of load current source, i.e. power dissipation. Figures 8 and 9 show simulation results without decoupling capacitor. In the uniform case of Fig. 8, error caused by ignoring on-chip inductance is about 10% of voltage fluctuation. This error may not affect circuit delay considerably. However, in the unbalance case of Fig. 9, ignoring on-chip inductance causes 35% estimation error, and it is not acceptable in circuit design.

Figure 10 explains the reason. When load current at each grid is the same, almost all current comes from the capacitance at the same grid. The amount of current that flows through the branch is

Figure 8: Voltage fluctuation in power grid: uniform case (at center of chip).

Figure 9: Voltage fluctuation in power grid: unbalance case (at center of chip).

very small. That is why on-chip inductance hardly affects voltage fluctuation when power consumption is uniform.

Let us discuss the unbalance case. In this case, almost all capacitances that placed on the chip work to suppress voltage fluctuation, if on-chip inductance is not considered. However, when we consider on-chip inductance, capacitances far from current source hardly help to reduce voltage fluctuations.

When power consumption is uniform, error caused by ignoring on-chip inductance is small. When current consumption is not uniform, analysis without on-chip inductance is not accurate enough. Normally, power consumption of LSI is not uniform, and hence we need to consider on-chip inductance.

### 4.2 With decoupling capacitors

In modern LSI design, LSI power distribution network has numerous decoupling capacitors. We evaluate effect of on-chip inductance in power network with decoupling capacitance. We append intentional decoupling capacitors to power distribution network according to a simple method to calculate required capacitance size [9].

We calculate the amount of decoupling capacitance to suppress voltage fluctuations below 10% of supply voltage. We simulate three power distribution circuits that have different amount of deIf load currents are the same or enough decap is available at each grid, current flowing through branch is very small.

These inductances hardly affect voltage fluctuation

Figure 10: Reason why on-chip inductance hardly affects voltage fluctuation.

Figure 11: Voltage fluctuation: uniform placement (at center of chip).

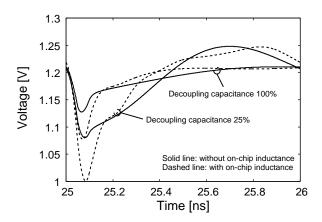

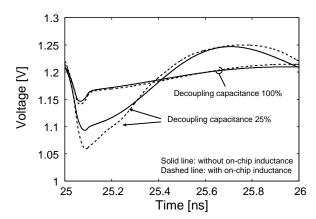

coupling capacitance; 25%, 50% and 100% of the calculated capacitance. Decoupling capacitors are placed in the following two strategies. One strategy places capacitors uniformly on the chip (uniform placement). In other words, this strategy does not consider power consumption distribution, but it performs chip-level capacitance insertion. The other strategy places large capacitor near large current source (adaptive placement). In both strategies, total amount of decoupling capacitance in the circuit is the same. We examine how the effect of on-chip inductance varies according to the design policy of decoupling capacitance in size and placement.

The method to calculate required decoupling capacitance [9] is briefly explained. Size of decoupling capacitor C is calculated from target of maximum voltage ripple  $\delta V$  and charge within one current cycle  $Q=I_{\rm p\,eak}\,Tr/2$ .

$$C = Q/\delta V. (4)$$

From this formula, in the case that capacitors are placed uniformly, capacitance of 12.3pF, which corresponds to MOS gate of  $1,000\mu\text{m}^2$ , is inserted at every 400 grid in the circuits. As for the adaptive placement, capacitance size varies from 6.15 to 30.7pF according to load current at each grid.

Figure 11 shows the results of the uniform placement case, and Figure 12 shows the result of the adaptive placement case. When decoupling capacitors is inserted according to the local load current and its size is enough (100% size in Fig. 12), the effect of on-chip inductance on voltage fluctuation is not significant. When decoupling capacitor size becomes smaller, ignoring on-chip in-

Figure 12: Voltage fluctuation: adaptive placement (at center of chip).

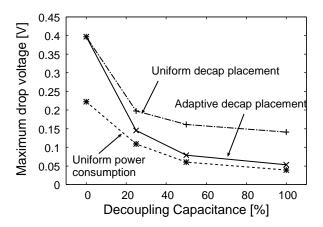

Figure 13: Size of decoupling capacitor and voltage fluctuation.

ductance causes a large amount of error. We can also see that the placement of decoupling capacitance is very important, comparing Fig. 11 with Fig. 12. Even if size of decoupling capacitors is large enough to suppress voltage fluctuation, the bad strategy of the uniform placement cannot suppress voltage fluctuation well.

Figure 13 shows the relationship between size of decoupling capacitance and the maximum voltage drop. When decoupling capacitors are placed by the adaptive placement, voltage fluctuation becomes smaller rapidly as capacitor size increases. In the case of the uniform placement, enlarging capacitance decreases voltage fluctuation similarly, however its suppression effect is smaller than that of the adaptive placement.

With decoupling capacitance whose size is large enough compared with local load current, ignoring on-chip inductance does not affect voltage fluctuation seriously. In this situation, almost all load current comes from the neighboring decoupling capacitor. This means that the current that flows through branches is small and hence the effect of on-chip inductance becomes small, which is similar with the discussion in the previous section (Fig. 10). As long as decoupling capacitor is well designed in size and placement, the accuracy of power analysis without on-chip inductance is acceptable. However, when estimation of load current is poor, the efficiency of decoupling capacitor insertion degrades and the effect of on-chip inductance becomes significant.

Figure 14: Comparison between PEEC and decoupled models.

Table 1: Voltage fluctuation and grid pitch

| Power grid pitch   | Maximum voltage fluctuation |

|--------------------|-----------------------------|

| 300μm              | 303mV                       |

| $150\mu\mathrm{m}$ | 280mV                       |

| $100\mu\mathrm{m}$ | 270mV                       |

| $50\mu\mathrm{m}$  | 245mV                       |

### 5. POWER GRID DESIGN FOR ROBUST-NESS WITH ON-CHIP INDUCTANCE

This section evaluates the effect of on-chip inductance varying grid pitch, and wire area for power distribution (Fig. 1) in order to design robust power distribution network. The previous sections use the equivalent circuit that considers all mutual inductances in PEEC model in order to accurately evaluate the impact of on-chip inductance. However, the size of power distribution grid that can be analyzed is limited, because the inductance matrix is very dense. To evaluate finer power grid, this section uses a simplified equivalent circuit model that does not include mutual inductance.

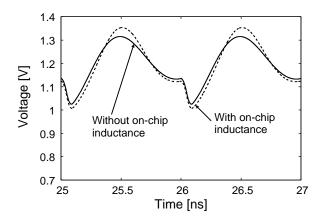

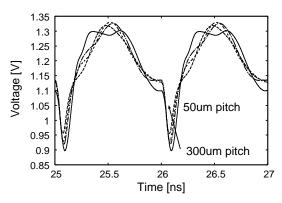

We first demonstrate the error due to the simplified circuit model. When current loop is perfectly closed in paired power/ground wires, the inductively-coupled power/ground wires can be decoupled into two wires whose self- and mutual inductances are L-M and 0. Figure 14 shows the noise waveforms when PEEC and decoupled models are used. The experimental condition is the same with that in the previous section. The decoupling capacitance is not attached. Though the waveforms are partly different in unbalanced current distribution, we use the decoupled model in the following experiments, because the error is not significant and the computational time is reduced by 98%.

### 5.1 Power grid pitch and wire area

We first change power grid pitch and evaluate the effect of onchip inductance while keeping the wire area of power grid unchanged. The wire resistance is determined by the wire area. On the other hand, inductance is not proportional to the wire area.

We change power grid pitch to  $50\mu m$ ,  $100\mu m$  and  $150\mu m$ , and compare power noise with that in  $300\mu m$  pitch case in the previous section. The wire area ratio of power grid is 20%, where the wire area ratio is defined as  $2\times$ (wire width)/(grid pitch). The spacing between paired power/ground wires is  $10\mu m$ . The other conditions are the same with those in the previous section. The current distribution is unbalanced. Figure 15, Table 1 show the results. Although the wire area is unchanged, the voltage fluctuation is reduced to 80% by changing grid pitch from  $300\mu m$  to  $50\mu m$ .

Figure 15: Power noise waveforms when grid pitch is changed.

Figure 16: Voltage fluctuation and wire area ratio (grid pitch  $300\mu m$ ).

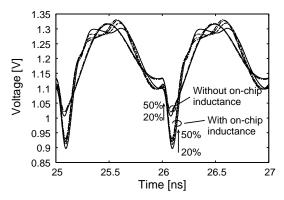

We next evaluate the effect of on-chip inductance when the wire area for power grid is varied. The variation of wire area ratio is 20%, 30%, 40% and 50%. The grid pitch is  $300\mu m$  and  $50\mu m$ . Figures 16, 17 show the simulation results. Figure 16 presents the voltage fluctuation when grid pitch is  $300\mu m$ , and Figure 17 corresponds to the result in the case of  $50\mu m$  grid pitch. When grid pitch is large, the increase in wire area ratio from 20% to 50% reduces voltage variation by 10% when on-chip inductance is considered, and by 7% without consideration of on-chip inductance (Fig. 16). The noise reduction ratio with consideration of on-chip inductance is somewhat larger. When grid pitch is small, the amount of noise reduction is 7% both with and without considering on-chip inductance (Fig. 17).

Thus, making grid pitch smaller is very effective to suppress voltage fluctuation. Although increase in wire area suppresses power noise, its availability is smaller than that of minifying the grid pitch.

### 5.2 Spacing between power and ground wires

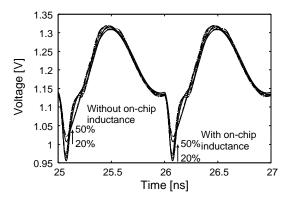

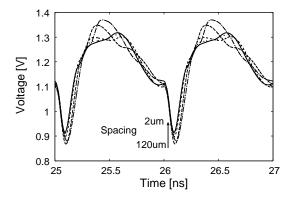

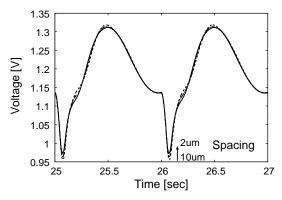

In the experiments shown so far, the spacing between power and ground wires are small. In this case, wire inductance becomes small, since the current loop becomes small [1]. We here evaluate how important the spacing is for power supply noise. We assume that power grid pitch is  $300\mu m$  and  $50\mu m$ . The thickness of wires is  $1\mu m$ , and the wire area ratio is 20%. We then vary spacing between power and ground wires to 2, 5, 10, 30, and  $120\mu m$ , and evaluate the voltage fluctuation, where the spacing of 30 and  $120\mu m$  is evaluated only when grid pitch is  $300\mu m$ .

Figure 17: Voltage fluctuation and wire area ratio (grid pitch  $50\mu m$ ).

Figure 18: Voltage fluctuation and spacing (grid pitch  $300\mu m$ ).

Figures 18, 19 show the noise waveforms. When grid pitch is  $300\mu$ m, the maximum noise voltage increases from 285mV to 320mV by changing the spacing from  $2\mu$ m to  $120\mu$ m. The variation ratio of noise voltage is  $\pm 5$ –6% compared with the noise of 303mV in the case of  $10\mu$ m spacing. The voltage fluctuation is also reduced by 8% when the spacing decreases to  $2\mu$ m in the case of  $50\mu$ m grid pitch.

These results demonstrate that the spacing between power and ground wires affects power supply noise as we expected, and indicate that we should minimize the spacing to suppress power supply noise.

### 6. CONCLUSION

In this paper, the effect of on-chip inductance in power distribution network is discussed. This paper shows that voltage fluctuations are enlarged by on-chip inductance. Only capacitors that are placed close to load current source contribute to suppress voltage fluctuation effectively.

We evaluate the effect of on-chip inductance on voltage fluctuation under a power consumption distribution like a real chip operation. When chip power consumption is uniform, error caused by ignoring on-chip inductance is small enough. Even if power consumption is not uniform, as long as decoupling capacitors are designed appropriately in placement and size, ignorance of on-chip inductance does not cause a significant error. When we design power network considering on-chip inductance, not only size of decoupling capacitors but also place of capacitors is crucial to enhance power supply integrity.

Figure 19: Voltage fluctuation and spacing (grid pitch  $50\mu m$ ).

We also examine the influence of grid pitch, wire area, and spacing between power and ground wires on voltage fluctuation. The results indicate that making grid pitch smaller is superior to increasing wire area in noise reduction effect. We also observe that smaller spacing between power and ground wires is preferable as we expected.

### 7. ACKNOWLEDGMENT

This work is supported in part by the 21st Century COE Program (Grant No. 14213201).

#### 8. REFERENCES

- A. V. Mezhiba and E. G. Friedman, "Power Distribution Networks in High Speed Integrated Circuits," *Kluwer Academic Publishers*, 2004.

- [2] Y.-M. Lee and C. C.-P. Chen, "Power Grid Transient Simulation in Linear Time Based on Transmission-Line-Modeling Alternating-Direction-Implicit Method," *IEEE Transactions on Computer-Aided Design*, Vol. 21, No. 11, pp.1343 -1352, Nov. 2002.

- [3] W. H. Lee, S. Pant and D. Blaauw, "Analysis and reduction of on-chip inductance effects in power supply grids," in *Proc. International Symposium on Quality Electronic Design*, 2004.

- [4] C. W. Fok and D. L. Pulfrey, "Full-chip power-supply noise: the effect of on-chip power-rail inductance," *International Journal of High Speed Electronics and Systems*, vol. 12, no. 2, pp. 573–582, 2002.

- [5] H. H. Chen and D. D. Ling, "Power supply noise analysis methodology for deep-submicron VLSI chip design," in *Proc. Design Automation Conference*, pp. 638–643, 1997.

- [6] K. Gala, D. Blaauw, J. Wang, V. Zolotov and M. Zhao, "Inductance 101: analysis and design issues," in *Proc. Design Automation Conference*, pp. 329–334, 2001.

- [7] A. Kurokawa, K. Hachiya, K. Tokumasu and H. Masuda, "Fast on-chip inductance extraction of VLSI including angled interconnects," *IEICE Trans. Fundamentals*, vol. E86-A, No. 4, pp. 841–845, Apr. 2003.

- [8] A. E. Ruehli, "Equivalent Circuit Models for Three-Dimensional Multiconductor Systems," *IEEE Trans.* MTT, Vol. MTT-22, No. 3, pp. 216–221, Mar 1974.

- [9] L. Smith, "Decoupling capacitor calculations for CMOS circuits," in *Proc. IEEE 3rd Topical Meeting of Electrical Performance of Electronic Packaging*, pp. 101–105, Nov. 1994.