# Asymptotic Waveform Evaluation for Timing Analysis

LAWRENCE T. PILLAGE, MEMBER, IEEE, AND RONALD A. ROHRER, FELLOW, IEEE

Abstract-For digital system designs the propagation delays due to the physical interconnect can have a significant, even dominant, impact on performance. Timing analyzers attempt to capture the effect of the interconnect on the delay with a simplified model, typically an RC tree. For mid-frequency MOS integrated circuits the RC tree methods can predict the delay to within 10 percent of a SPICE simulation and at faster than 1000x the speed. With continual progress in integrated circuit processing, operating speeds and new technologies are emerging that may require more elaborate interconnect models. Digital bipolar and high-speed MOS integrated systems can require interconnect models which contain coupling capacitors and inductors. In addition. to enable timing verification at the printed circuit board level also requires general RLC interconnect models. Asymptotic Waveform Evaluation (AWE) provides a generalized approach to linear RLC circuit response approximations. The RLC interconnect model may contain floating capacitors, grounded resistors, inductors, and even linear controlled sources. The transient portion of the response is approximated by matching the initial boundary conditions and the first 2q-1 moments of the exact response to a lower order q-pole model. For the case of an RC tree model a first-order AWE approximation reduces to the RC tree methods.

## I. Introduction

WITH FINER feature sizes and higher signal speeds, systems that are designed to be digital may evidence aspects of analog behavior in their interconnect, which become the ultimate determinants of performance. Timing analyzers [1]-[4] and timing simulators [5], [6] attempt to capture the effect of the interconnect on the delay to produce reliable timing verification. For many MOS circuits, timing analyzers [1], [3] are often able to predict the interconnect delay with a simplified model, typically an RC tree [7], to within 10 percent of a SPICE [8] simulation prediction. RC trees are RC circuits with capacitors from all nodes to ground, no floating capacitors, no resistor loops, and no resistors to ground. The signal delays through an RC tree are often estimated using a form of the Elmore delay [9], which provides a dominant time constant approximation for monotonic step responses.

To enable the timing verification of bipolar circuits, the

Manuscript received September 6, 1988; revised April 24, 1989. This work was supported in part by Digital Equipment Corporation and the Semiconductor Research Corporation. This paper was recommended by Associate Editor R. K. Brayton.

- L. T. Pillage is with the Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX 78712.

- R. A. Rohrer is with the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA 15213.

IEEE Log Number 8933519.

interconnect model may need to include grounded resistors [10] and inductors [11] which are not compatible with RC trees. Even for MOS circuits at particularly high speeds, the effects of coupling capacitance may need to be included in the delay estimate. Particularly at the printed circuit board level, input voltage rise time can dominate the timing of a net thus precluding the use of step response approximations for delay estimation. Moreover, for generality, a solution is required when there are nonequilibrium initial conditions so that the delays due to charge sharing effects can be predicted.

RLC circuits with nonequilibrium initial conditions may have response waveforms which are nonmonotonic. A single time constant approximation with the Elmore delay is not generally applicable for such circuits. Two time constant models have been shown to improve the accuracy [12], where they too have been applied to RC tree monotone response approximations. Asymptotic Waveform Evaluation (AWE) provides a generalized approach to waveform estimation for RLC circuits with initial conditions and nonzero input signal risetimes. The RLC circuits may contain floating capacitors, grounded resistors, inductors, and linear controlled sources. The transient response of an RLC circuit is approximated by matching the initial boundary conditions and the first 2q-1 moments of the actual response to a lower order q-pole model. For the case of an RC tree driven by a step input, a first-order AWE approximation is equivalent to the methods which employ Elmore's delay expression.

Section II begins with a discussion of previous work in delay estimation for timing analysis. The RC tree methods which employ Elmore's delay expression are briefly reviewed. For a more detailed summary of the previous work refer to [11]. Next, AWE is described in general in terms of state variable analysis. The state variable formulation is used only to explain AWE as applied in general to RLC circuits. Then in Section IV the practical procedural steps of AWE are described and related to the RC tree methods. Finally, examples of AWE are provided for a variety of RLC interconnect circuit models, followed by our concluding remarks in Section VI.

## II. RC TREE METHODS

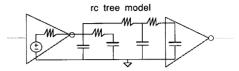

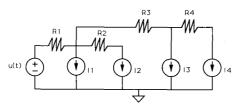

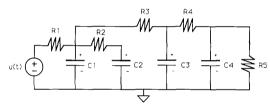

A typical approach to timing analysis of MOS integrated circuits is to divide the design into stages, with each stage consisting of a gate output and the interconnect

path which it drives. A simple example of a stage is shown in Fig. 1. The RC tree approach to delay estimation of this stage models the MOSFETs in terms of linear approximate resistors and capacitors determined as functions of their process parameters and the voltage changes which are to appear across their gates [1], [3], [5], [6]. The interconnect is modeled by an RC tree network. An RC tree is an RC network with a capacitor from each node to ground, no floating capacitors, no resistor loops, and no resistors to ground. The MOS circuit delay is then estimated in terms of the delay through the RC tree model. The more popular methods of estimating the delay through these linear RC trees will be reviewed in this section.

## 2.1. Delay Estimation for Linear RC Trees

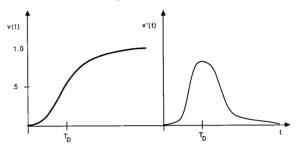

There are many definitions of delay given the actual transient response. The most straightforward is the time at which the output transient rises to 50 percent of its final value, as shown in Fig. 2. Elmore [9] proposed an expression for approximating the time,  $T_D$ , at which the transient step response would reach 50 percent of its final value for monotonic waveforms. Elmore's expression approximates the mid-point of the monotone step response waveform by the mean, or first moment, of the impulse response:

$$T_D = \int_0^\infty t \dot{v} \, dt. \tag{1}$$

Since v(t) is monotone, its first derivative, the impulse response, will always be of the form of a probability density function as shown in Fig. 2. The mean of the distribution given by  $\dot{v}(t)$  is a good approximation for the 50-percent point of the transient portion of v(t). For an RC tree, Elmore's expression can be applied since the step response waveforms are always monotone [7].

The Elmore delay provides a single value for the delay estimate,  $T_D$ . Such an estimate does not consider the logic thresholds of actual MOS device. To do so requires finding an approximating response waveform and determining the time at which the logic threshold is crossed [11]. The Elmore delay, or first moment of the impulse response, is also a good approximation for the dominant time constant of the step response [11]. Penfield and Rubenstein [7] applied the Elmore delay as a dominant time constant approximation to determine the nominal delay from a single exponential function with  $T_D^{-1}$  as the pole.

$$v(t) \approx v(\infty) (1 - e^{-t/T_D}). \tag{2}$$

The Elmore delay can be found by inspection as a summation of series path resistance and shunt capacitance values when the circuit is restricted to the configuration of an RC tree [7], [11]. The Elmore delay expressed as a summation of R's and C's can also be bounded for worst-and best-case responses [7], [14]. As in the original [9], only step inputs are considered and initial conditions are assumed to be zero.

Fig. 1. RC tree model of a simple logic stage.

Fig. 2. Example of a monotonic step response and its derivative.

## 2.2. Grounded Resistors

RC tree methods were extended to circuit configurations which contain loops of resistors [11]. The Elmore delay for these RC meshes is calculated and applied as before. To enable delay evaluation for bipolar circuits, the RC tree models were further extended to include grounded resistors. Resistance to ground requires that the steady state be obtained and that the delay value be scaled by the magnitude of the voltage transition. This extension has been presented in [10], [15], [16] independently, all of which result in an expression similar to

$$T_D = \frac{1}{v(\infty) - v(0)} \int_0^\infty \left[ v(\infty) - v(t) \right] dt. \quad (3)$$

## 2.3. Nonequilibrium Initial Conditions

Lin and Mead [5] extended the Elmore definition to evaluate the delay for nonmonotone step response waveforms. The circuit configurations were again restricted to *RC* meshes but now equilibrium initial conditions, which generate nonmonotone response waveforms, were admissable. The nonmonotone response waveforms were not predicted, but only a delay value was obtained.

Chu and Horowitz [12], [17] developed a two-pole model for analysis of *RC* meshes with similar nonequilibrium initial conditions to consider charge sharing effects. Consistent with Elmore's definition, however, only monotone response waveforms were considered.

# 2.4. Comments on Previous Work

These RC tree approaches to timing estimation have been used successfully for timing analysis [1]-[3] and

timing simulation [5], [6] of low- to mid-frequency MOS digital integrated circuits. The single time-constant and double time-constant models provide good delay estimates for RC tree paths when driven by step inputs; higher order approximations may be required, however, when inductance and floating capacitance effects are not negligible. Although nonequilibrium initial conditions are considered for the one- and two-pole models, they are valid for a limited set of conditions and may be unable to provide a means of handling the nonmonotone waveforms which may result in general.

## III. ASYMPTOTIC WAVEFORM EVALUATION (AWE)

Timing analysis of more general digital circuits may require models more elaborate than *RC* trees driven by single step inputs. Analysis of *RLC* interconnect circuit models with initial conditions and nonmonotone response waveforms requires a more comprehensive waveform estimator. AWE is a generalized approach to approximating the waveform response of linear circuits with multiple step and ramp input signals and unrestricted nonequilibrium initial conditions.

## 3.1. The AWE Approximation

AWE is most conveniently explained in general in terms of the differential state equations for a lumped, linear, time-invariant circuit:

$$\dot{x} = Ax + Bu \tag{4}$$

where x is the n-dimensional state vector and u is the m-dimensional excitation vector. In all but the most pathological cases such a circuit description exists [18]. Once AWE is explained in general, the results will be particularized to the more familiar RC tree circuits for comparison with the present practices of delay estimation from the previous section.

Suppose that the particular excitation is of the form

$$u_n(t) = u_0 + u_1 t, \quad t \ge t_0$$

(5)

where  $u_0$  and  $u_1$  are constant *m*-dimensional vectors. In general the form of  $u_p(t)$  need not be confined to such simple signals, but rather could assume any form of input excitation for which a particular solution can easily be obtained. Inputs that are polynomials in time or sums of complex-valued exponentials can in theory be as easily accommodated as the step/ramp combination in expression (5). For present purposes this simple class of input excitations is considered because it is adequate for the investigation of delay and rise time effects.

For the excitation  $u_p$ , (5), the differential-state equations (4) has the particular solution

$$\mathbf{x}_{n}(t) = -\mathbf{A}^{-1}\mathbf{B}\mathbf{u}_{0} - \mathbf{A}^{-2}\mathbf{B}\mathbf{u}_{1} - \mathbf{A}^{-1}\mathbf{B}\mathbf{u}_{1}t.$$

(6)

The A-matrix may not be singular for this particular solution to exist. This condition is equivalent to specifying that the circuit in question have a unique and well-defined dc solution when all of its capacitances are open-circuited and all of its inductances are short-circuited. This is not

an unreasonable restriction for most of the circuits for which delay estimation may be of interest. There are situations, however, when a node is isolated such that it is connected to the supply voltage only through capacitors. The steady-state solution for these floating nodes must be determined by the charge conservation equation. Assuming for now that there are no floating nodes in the circuit, we complete the solution of (4) with the homogeneous equation:

$$\dot{\mathbf{x}}_h = \mathbf{A}\mathbf{x}_h \tag{7}$$

now with the initial condition

$$x_h(0) = x_0 + A^{-1}Bu_0 + A^{-2}Bu_1$$

(8)

where  $x_0$  is the initial state at time zero. The Laplace transform solution of the homogeneous equation is

$$X_h(s) = (sI - A)^{-1} x_h(0). (9)$$

To approximate this solution,  $X_h(s)$  is first expanded in a Maclaurin series

$$X_h(s) = -A^{-1}(I + A^{-1}s + A^{-2}s^2 + \cdots) x_h(0)$$

(10)

and as many moments as necessary or desirable are matched in terms of lower order approximating functions. The justification for such a moment matching approach follows from the Laplace transform definition

$$X(s) = \int_0^\infty e^{-st} x(t) dt = \sum_{k=0}^\infty \frac{1}{k!} (-s)^k \int_0^\infty t^k x(t) dt$$

(11)

since it has long been established that the time moments:

$$m_k = \frac{(-1)^k}{k!} \int_0^\infty t^k x(t) \, dt, \tag{12}$$

provide excellent measures of delays, rise times, etc. [9], [19]. Focusing for now on a specific component of  $X_h(s)$ , say the *i*th, its initial conditions and first 2q-1 moments (from (10)) are characterized as

$$[\mathbf{m}_{-1}]_{i} = [x_{h}(0)]_{i}$$

$$[\mathbf{m}_{0}]_{i} = [-\mathbf{A}^{-1}\mathbf{x}_{h}(0)]_{i}$$

$$[\mathbf{m}_{1}]_{i} = [-\mathbf{A}^{-2}\mathbf{x}_{h}(0)]_{i}$$

$$\vdots \qquad \vdots$$

$$[\mathbf{m}_{2q-2}]_{i} = [-\mathbf{A}^{-2q+1}\mathbf{x}_{h}(0)]_{i}.$$

(13)

It is these moments that are matched to a lower order frequency-domain function of the form

$$\hat{X}_{i}(s) = \frac{k_{1}}{s - p_{1}} + \frac{k_{2}}{s - p_{2}} + \dots + \frac{k_{q}}{s - p_{q}}$$

$$= \sum_{l=1}^{q} \frac{k_{l}}{s - p_{l}} = -\sum_{i=1}^{q} \frac{k_{l}/p_{l}}{1 - s/p_{l}}$$

(14)

where  $p_1$  through  $p_q$  are the complex approximating poles and  $k_1$  through  $k_q$  their appropriate residues. In other words, the time-domain moments are to be matched to those of an approximating function of the form

$$\hat{x}_{i}(t) = \sum_{l=1}^{q} k_{l} e^{p_{l}t}.$$

(15)

Under the assumption that the moments (13) can be generated easily—more on this when computational considerations are discussed—what remains now is to solve for the time constants and their corresponding residues. Expanding each of the terms in (14) into a series about the origin, and upon inclusion of the initial conditions, the following set of nonlinear simultaneous equations for the *i*th state variable is obtained:

$$-(k_{1} + k_{2} + \cdots + k_{q}) = [\mathbf{m}_{-1}]_{i}$$

$$-\left(\frac{k_{1}}{p_{1}} + \frac{k_{2}}{p_{2}} + \cdots + \frac{k_{q}}{p_{q}}\right) = [\mathbf{m}_{0}]_{i}$$

$$-\left(\frac{k_{1}}{p_{1}^{2}} + \frac{k_{2}}{p_{2}^{2}} + \cdots + \frac{k_{q}}{p_{q}^{2}}\right) = [\mathbf{m}_{1}]_{i}$$

$$\vdots \qquad \vdots$$

$$-\left(\frac{k_{1}}{p_{1}^{2q-1}} + \frac{k_{2}}{p_{2}^{2q-1}} + \cdots + \frac{k_{q}}{p_{q}^{2q-1}}\right) = [\mathbf{m}_{2q-2}]_{i}.$$

(16)

A solution for the approximating poles and residues from this set of nonlinear equations could proceed in terms of Newton-Raphson [20] or a similar iteration method. The complexity of these indirect solution methods, however, is not fixed, but varies with the problem. Moreover, heuristics are needed to monitor the iteration step size to control convergence.

Instead of attempting to solve the nonlinear equations given by (16), we will reformulate the problem to allow for direct solution of the approximating poles and residues. The set of equations in (16) can be summarized in matrix form as

$$-\nabla k = [m_l]_i \tag{17}$$

and

$$\nabla \mathbf{\Lambda}^{-q} \mathbf{k} = [\mathbf{m}_h], \tag{18}$$

where  $m_i$  represents the low-order moments  $(-1, 0, \dots, q-2)$ ,  $m_h$  represents the high-order moments  $(q-1, q, \dots, 2q-2)$ ,  $\Lambda^{-1}$  is a diagonal matrix of the reciprocal complex poles, and  $\nabla$  is the well-known Vandermonde matrix [21]:

$$\begin{bmatrix} 1 & 1 & \cdots & 1 \\ p_1^{-1} & p_2^{-1} & \cdots & p_q^{-1} \\ p_1^{-2} & p_2^{-2} & \cdots & p_q^{-2} \\ \vdots & \vdots & & \vdots \\ p_1^{-q+1} & p_2^{-q+1} & \cdots & p_q^{-q+1} \end{bmatrix}.$$

(19)

It follows then from (17) that

$$\mathbf{k} = -\mathbf{\nabla}^{-1} \mathbf{m}_{t} \tag{20}$$

and

$$\nabla \Lambda^{-q} \nabla^{-1} \mathbf{m}_l = \mathbf{m}_h. \tag{21}$$

Since the Vandermonde matrix is the modal matrix for a system matrix in companion form [19], (21) is equivalent to

$$\boldsymbol{A}_{c}^{-q}\boldsymbol{m}_{l}=\boldsymbol{m}_{h} \tag{22}$$

where

$$A_c^{-1} = \begin{bmatrix} 0 & 1 & 0 & \cdots & 0 \\ 0 & 0 & 1 & \cdots & 0 \\ \vdots & \vdots & \vdots & & \vdots \\ -a_0 & -a_1 & -a_2 & \cdots & -a_{q-1} \end{bmatrix}$$

(23)

with the coefficients normalized so that  $a_q = 1$ . This matrix is characterized as  $A_c^{-1}$  rather than  $A_c$  because its eigenvalues are the reciprocals of the approximating poles for the original system (4). It is shown in [22] that the set of simultaneous nonlinear equations (22) for the coefficients  $a_0$  through  $a_{q-1}$ ,  $a_c$ , can be written recursively to yield the following set of linear equations:

$$\begin{bmatrix} m_{-1} & m_0 & \cdots & m_{q-2} \\ m_0 & m_1 & \cdots & m_{q-1} \\ \vdots & \vdots & & \vdots \\ m_{q-2} & m_{q-1} & \cdots & m_{2q-3} \end{bmatrix} \begin{bmatrix} -a_0 \\ -a_1 \\ \vdots \\ -a_{q-1} \end{bmatrix} = \begin{bmatrix} m_{q-1} \\ m_q \\ \vdots \\ m_{2q-2} \end{bmatrix}.$$

(24)

It is in terms of  $a_c$  that we can form a characteristic polynomial

$$a_0 + a_1 p^{-1} + a_2 p^{-2} + \cdots + a_{q-1} p^{-q+1} + p^{-q} = 0$$

(25)

the roots of which are the reciprocals of the desired poles.

If the poles are not distinct, the Vandermonde matrix is by definition singular. For such cases the residues must be found using an expression other than (20). For the case of a double pole given a second-order approximation:

$$\hat{X}(s) = \frac{k_1}{(s - p_1)^2} + \frac{k_1}{s - p_1}.$$

(26)

Expanding the terms in (26) into a series about s = 0:

$$\hat{X}(s) = \frac{k_1}{p_1^2} \left( 1 + \frac{2s}{p_1} + \frac{3s^2}{p_1^2} + \frac{4s^3}{p_1^3} + \cdots \right) + \frac{k_1}{p_1} \left( 1 + \frac{s}{p_1} + \frac{s^2}{p_1^2} + \cdots \right). \tag{27}$$

From (27) it is apparent that the poles and residues are related to the moments by

$$\begin{bmatrix} p_1^{-2} & p_1^{-1} \\ 2p_1^{-3} & p_1^{-2} \end{bmatrix} \begin{bmatrix} k_1 \\ k_2 \end{bmatrix} = \begin{bmatrix} m_{-1} \\ m_0 \end{bmatrix}.$$

(28)

More generally, for an *r*-order root, the approximate residues are related to the approximate poles by

time invariant circuit takes the following form [18]:  $\begin{bmatrix} C & 0 \end{bmatrix}^{-1} \begin{bmatrix} H_{12} & H_{22} \end{bmatrix}$

$$\mathbf{A} = \begin{bmatrix} \mathbf{C} & \mathbf{0} \\ \mathbf{0} & \mathbf{L} \end{bmatrix}^{-1} \begin{bmatrix} \mathbf{H}_{CC} & \mathbf{H}_{CL} \\ \mathbf{H}_{LC} & \mathbf{H}_{LL} \end{bmatrix}. \tag{31}$$

The C and L submatrixes are symmetric diagonally dominant descriptions of the capacitance and inductance portions of the circuit. If there are no capacitance-voltage

$$\begin{bmatrix} (-1)^{r} & (-1)r - 1 & \cdots & -1 \\ p^{-r} & p^{-(r-1)} & \cdots & p^{-1} \\ \frac{r!}{(r-1)!} p^{-(r+1)} & \frac{(r-1)!}{(r-2)!} p^{-(r)} & \cdots & p^{-2} \\ \frac{r+1)!}{(r-1)!2!} p^{-(r+2)} & \frac{(r)!}{(r-2)!2!} p^{-(r+1)} & \cdots & p^{-3} \\ \vdots & \vdots & & \vdots \\ \frac{(2r-2)!}{(r-1)!(r-1)!} p^{-(2r-1)} & \frac{(2r-3)!}{(r-2)!(r-1)!} p^{-(2r-2)} & \cdots & p^{-r} \end{bmatrix}$$

$$(29)$$

Expression (24) can still be applied in cases of repeated poles to find the approximating characteristic polynomial. This expression arises also in the model order reduction problem much studied in linear control system theory [23]. Typically in control theory the model-order reduction problem is stated first in terms of a rational transfer function

$$\hat{X}(s) = \frac{1 + b_1 s + b_2 s^2 + \dots + b_m s^m}{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}$$

(30)

to which a lower order rational transfer function approximation is sought. For the case of m = n - 1, matching the moments from the expansion of (30) to the first m + n + 1 circuit moments results in expression (24) [23].

To summarize, determining the set of q approximating poles and residues from the moments requires first: solving a qth-order set of linear equations (24) by Gaussian elimination to find  $a_c$ ; then solving for the roots of  $a_c$  from (25) to determine the approximating poles; and finally determining the residues by solving the q simultaneous linear equations from expression (20) (or (29) for the repeated root case). For the low orders of approximation that are needed for the intended application of AWE, the roots of  $a_c$  can be obtained explicitly, and the complexity of the solutions for (20) and (24) is modest at  $\Theta(q^3)$ . In such cases the runtime is dominated by the calculation of the moments.

## 3.2. Complexity

The computation of the powers of  $A^{-1}$  to obtain the moments (13) may look to be more complicated than it actually is. In general the A-matrix for a lumped, linear,

source loops or no inductance-current source cutsets in the circuit, these submatrices reduce, respectively, to diagonal. The  $\boldsymbol{H}$  matrix in (31) is merely the hybrid characterization of the dc circuit that results upon zeroing all original independent sources and forming ports appropriately for the energy storage elements [18].

It follows that  $A^{-1}$  is

$$\boldsymbol{A}^{-1} = \begin{bmatrix} \boldsymbol{H}_{CC} & \boldsymbol{H}_{CL} \\ \boldsymbol{H}_{LC} & \boldsymbol{H}_{LL} \end{bmatrix}^{-1} \begin{bmatrix} \boldsymbol{C} & \boldsymbol{0} \\ \boldsymbol{0} & \boldsymbol{L} \end{bmatrix}. \tag{32}$$

It is advantageous in practice that the *energy storage* matrix need not be inverted to find  $A^{-1}$  since the models which result from circuit extraction may include many parasitic energy storage elements with large variations in magnitude among them.

The moments are computed recursively:

$$\boldsymbol{m}_{-1} = \boldsymbol{x}_h(0) \tag{33}$$

and

$$m_{k+1} = A^{-1}m_k$$

, for  $k = (0, 1, \dots, 2q - 2)$ .

The energy storage matrix is sparse, symmetrical, and easily applied. So once the *H*-matrix is LU-factored the major task in computing even higher moments is repeated forward- and back-substitution of these LU-factors. Even the *LC*-factorization is not formidable. Such an analysis must be performed in any case to obtain the steady-state solution. Moreover, in the following section it is shown that for several interconnect circuit models, *RC* trees included, the LU factors need not be found at all.

### 3.3. Stability

Expression (24) is one of many alternative moment matching methods that may be employed to obtain the approximating poles [23]-[26]. AWE differs from those of control system theory in that the zeros are not found directly, but rather the residues are obtained in order to approximate the time response. More importantly, AWE differs in that the particular solution is subtracted a priori and only the transient portion of the response is approximated. By focusing on the residues and the homogeneous response, the lower order approximation can be forced to match the initial state,  $m_{-1}$ , and the finite integral of the voltage response,  $m_0$ . Since the integral of the approximating voltage waveform is finite and equal to the exact, the final value must also match that of the exact, thus stability in guaranteed.

There are instances when the homogeneous response waveform is nonmonotone and a low-order approximation cannot match the integral of the voltage,  $m_0$ . The low-order AWE approximation may prove in such cases to have no solution, or may result in a positive approximating pole. These situations are easily remedied by moving to the higher order of approximation necessitated.

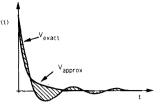

#### 3.4. Accuracy

The accuracy measure refers to how well the AWE qthorder model approximates the nth order circuit response. For our purposes, the accuracy is ideally measured by the difference between the approximate response waveform and the exact output waveform over the time range of interest. Referring to Fig. 3, the accuracy is a measure of the shaded region.

The error indicated in Fig. 3 can be expressed simply in terms of the integral of the squared waveform difference:

Error =

$$\sqrt{\int_0^\infty \left[v_{\text{exact}}(t) - \hat{v}(t)\right]^2 dt}$$

(35)

where  $\hat{v}(t)$  is the qth-order AWE approximation. Assuming that all of the approximate poles are real:

$$\hat{v}(t) = \sum_{i=1}^{q} \hat{k}_i e^{\hat{p}_i t}.$$

(36)

The relative error can be found by normalizing (35) by

$$\sqrt{\int_0^\infty \left[v_{\text{exact}}(t)\right]^2 dt}.$$

(37)

Of course, the exact response is not available for determining the error from (35). Instead we intend to approximate the error term by replacing the exact response in (35) with the q + 1 order AWE approximation:

$$v(t) = \sum_{i=1}^{q+1} k_i e^{p_i t}.$$

(38)

Fig. 3. The shaded region can be used to indicate the accuracy.

The approximate normalized error expression is

Error =

$$\sqrt{\frac{\int_{0}^{\infty} \left(\sum_{i=1}^{q+1} k_{i} e^{p_{i}t} - \sum_{i=1}^{q} \hat{k}_{i} e^{\hat{p}_{i}t}\right)^{2} dt}}{\int_{0}^{\infty} \left(\sum_{i=1}^{q+1} k_{i} e^{p_{i}t}\right)^{2} dt}}.$$

(39)

Calculating the error from (39) can be computationally intensive when the order of the approximation is large. For example, when q is equal to 4, evaluating the numerator term in (39) may require more than 40 potentially complex multiplication and addition operations. To reduce the complexity we solve for an upper bound on the numerator term using Cauchy's inequality [27]:

$$\left(\sum_{i=1}^{q+1} k_i e^{p_i t} - \sum_{i=1}^{q} \hat{k}_i e^{\hat{p}_i t}\right)^2 \\

\leq (q+1) \sum_{i=1}^{q+1} (k_i e^{p_i t} - \hat{k}_i e^{\hat{p}_i t})^2.$$

(40)

It follows that

$$\int_{0}^{\infty} \left( \sum_{i=1}^{q+1} k_{i} e^{p_{i}t} - \sum_{i=1}^{q} \hat{k}_{i} e^{\hat{p}_{i}t} \right)^{2} dt$$

$$\leq (q+1) \sum_{i=1}^{q+1} \int_{0}^{\infty} \left( k_{i} e^{p_{i}t} - \hat{k}_{i} e^{\hat{p}_{i}t} \right)^{2} dt. \tag{41}$$

Cauchy's formula is exact when the individual exponential terms of v(t) and  $\hat{v}(t)$  match up exactly. Therefore, to determine the least pessimistic result from (39), the individual v(t) and  $\hat{v}(t)$  terms should be paired in (41) by the poles and residues which lie closest to one another. In addition to ordering the poles, there must also be a way to match q+1 terms from v(t) with only q terms from  $\hat{v}(t)$ . The most straightforward approach is to match the first q-1 terms by pole and residue values as described above, leaving only the final three terms  $v_q$ ,  $v_{q+1}$  and  $\hat{v}_q$ . These terms can be matched as before by splitting the  $v_q$  term into two parts and evaluating:

$$\int_{0}^{\infty} \left( k_{q} e^{p_{q}t} - k_{q} e^{\hat{p}_{q}t} \right)^{2} dt \tag{42}$$

and

$$\int_{0}^{\infty} \left( k_{q+1} e^{p_{q+1}t} - (\hat{k}_{q} - k_{q}) e^{\hat{p}_{q}t} \right)^{2} dt.$$

(43)

Since (40) is valid only for real functions, the integrals of the individual differences

$$E_{i} = \int_{0}^{\infty} \left( k_{i} e^{p_{i}t} - \hat{k}_{i} e^{\hat{p}_{i}t} \right)^{2} dt \tag{44}$$

must be real numbers. Equation (44) can be shown to result in the expression:

$$E_{i} = -\frac{k_{i}^{2}}{p_{i}} - \frac{\hat{k}_{i}^{2}}{\hat{p}_{i}} + \frac{2k_{i}\hat{k}_{i}}{p_{i} + \hat{p}_{i}}.$$

(45)

When the AWE approximation contains complex pole pairs, they are evaluated in pairs so that the individual term differences are real functions and Cauchy's inequality still applies [22]:

$$E = \int_0^\infty \left( k e^{pt} + k * e^{pt} - \hat{k} e^{\hat{p}t} - \hat{k} * e^{\hat{p}t} \right)^2 dt. \quad (46)$$

At times, due to the difference in orders (q + 1 versus q), it may be necessary to compare a complex pole pair function with a single real pole function. This integral difference also results in a real function of the poles and residues [22].

The error term given by (39) is used only to measure the accuracy of the approximation. Instead of attempting to bound the response waveforms, which becomes more difficult as the approximation order is increased, we approximate quickly the accuracy and move to higher orders as required.

## 3.5. Frequency Scaling

In addition to the error associated with the AWE approximation, there is also the question of roundoff error. When the eigenvalues of  $A^{-1}$  are very small, or very large, the powers of  $A^{-1}$ , and therefore, the moments, change very rapidly. The large variation in moment values may cause the moment matrix in (24) to become ill-conditioned and near singular. For such cases, higher orders of approximation cannot be obtained unless the moment values are scaled.

As is done classically when working in the frequency domain [19] where values may range from 10<sup>2</sup> to 10<sup>8</sup> Hz or more, the frequency is scaled to first find a normalized solution, from which the normalized poles are scaled back to find the desired approximation. In AWE the normalization is chosen about the first pole by selecting a scale factor of

$$\gamma = \frac{m_{-1}}{m_0}.\tag{47}$$

Without frequency scaling, the moment matrix in (24) can become numerically unstable before an accurate solution may be reached.

# IV. RELATION TO RC TREE METHODS

To demonstrate that AWE does not imply excessive arithmetic, it is applied to the linear *RC* tree delay estimation problem from which it evolved. It will be shown

that in general, a first-order AWE approximation for an RC tree yields the Elmore delay as the reciprocal dominant pole with effort equivalent to that entailed for RC trees.

# 4.1. First-Order AWE Approximation

Finding  $A^{-1}$  from the state equations (4) is equivalent to solving for the port voltages of the open-circuit capacitance ports and short-circuit inductance ports [18]. For many circuit configurations, RC trees included, solving for these port variables is trivial.

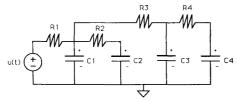

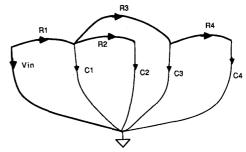

Consider as an example the RC tree shown in Fig. 4. The state equations for this RC circuit can be expressed in matrix form as

$$\dot{\boldsymbol{v}} = \boldsymbol{C}^{-1}\boldsymbol{G}\boldsymbol{v} + \boldsymbol{C}^{-1}\boldsymbol{B}\boldsymbol{u}(t) \tag{48}$$

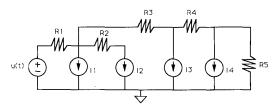

where u(t) is a unit step input voltage from 0 to  $V_{ss}$ , C is the diagonal capacitance matrix, and G is the related port conductance matrix. The steady state and the moments for this circuit can be obtained from the circuit in Fig. 5, where all the capacitors in Fig. 4 have been replaced by current sources. The steady state, or  $m_{-1}$  is obtained by setting  $\dot{v}$  equal to zero in (48) and solving for the capacitor voltages. This solution is equivalent to opening all the current sources I in Fig. 5 and obtaining the voltages across them.

The homogeneous solution to (48) is (from (10))

$$\boldsymbol{v}_h(s) = -\boldsymbol{G}^{-1}\boldsymbol{C}(\boldsymbol{I} + \boldsymbol{G}^{-1}\boldsymbol{C}s + \boldsymbol{G}^{-2}\boldsymbol{C}^2s^2 + \cdots)$$

$$\cdot (-\boldsymbol{v}_{ss}(0)). \tag{49}$$

The  $m_0$  moment is obtained by setting u(t) equal to zero and  $\dot{\boldsymbol{v}}$  equal to  $\boldsymbol{C}\boldsymbol{v}_{ss}(0)$  and solving for  $\boldsymbol{v}$  from (48). This solution is equivalent to setting I in Fig. 5 equal to  $-Cv_{ss}(0)$  and u(t) equal to zero, then obtaining the node voltages. Only  $m_{-1}$  and  $m_0$  are needed for a first-order approximation, but succeeding moments could be found by similar recursion if higher orders of approximation were sought. The next moment,  $m_1$ , can be obtained by setting I equal to  $Cm_0$  with u(t) = 0 and solving for the node voltages, and so on. Thus finding the moments of the actual circuit in Fig. 4 is a succession of dc solutions to the circuit in Fig. 5. The equations describing this dc circuit must be formulated and solved only once to determine the steady state. Solution for the moments then requires only changing the dc inputs for the new dc solution.

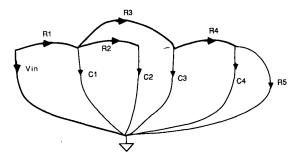

Since solving for the circuit moments requires only successive dc analyses, in practice the state equations are not formulated. Moreover, for simple circuits such as RC trees, the steady-state solution is explicit and the first moment, or Elmore delay can be determined by a tree walk of the circuit graph [7]. A graph representing the circuit in Fig. 5 is shown in Fig. 6. The voltage sources and the resistors form a spanning tree, i.e., a graph that touches all nodes but forms no cycles. In [7] it was shown that calculation of the first moment for any node is  $\Theta(n)$ ,

Fig. 4. RC tree example circuit.

Fig. 5. Capacitors in the circuit of Fig. 4 are replaced by current sources

where n is the number of capacitors. The Elmore delay at  $C_4$  as calculated from the graph is

$$T_D^4 = (R_1 + R_3 + R_4) C_4 + (R_1 + R_3) C_3 + R_1 C_2 + R_1 C_1.$$

(50)

A tree walk is viable for RC trees, but does not provide for a general analysis of paths with floating capacitance or inductance. With AWE, tree link analysis [28] is employed to solve for the moments since it enables a solution for all circuit topologies. It will be shown for the case of an RC tree, however, that tree link analysis provides for a generalized tree walk. For the RC tree in Fig. 5, the spanning tree in Fig. 6 is equivalent to the fundamental

$$v_{l} = \begin{bmatrix} -R_{1} & -R_{1} & -R_{1} & -R_{1} \\ -R_{1} & -(R_{1} + R_{2}) & -R_{1} & -R_{1} \\ -R_{1} & -R_{1} & -(R_{1} + R_{3}) & -(R_{1} + R_{3}) \\ -R_{1} & -R_{1} & -(R_{1} + R_{3}) & -(R_{1} + R_{3} + R_{4}) \end{bmatrix} \begin{bmatrix} I_{1} \\ I_{2} \\ I_{3} \\ I_{4} \end{bmatrix} - \begin{bmatrix} u(t) \\ u(t) \\ u(t) \\ u(t) \end{bmatrix}.$$

tree which uniquely specifies the tree link equations. From these equations the circuit moments can also be obtained in linear time. The tree link graph in Fig. 6 has the following fundamental loop/cutset matrix F[28]:

$$\begin{bmatrix} -1 & -1 & -1 & -1 \\ 0 & -1 & 0 & 0 \\ 0 & 0 & -1 & -1 \\ 0 & 0 & 0 & -1 \end{bmatrix}.$$

(51)

Fig. 6. Tree link graph for the RC circuit in Fig. 4.

The overall solution for the circuit of Fig. 5 can be obtained easily in terms of either the tree branch voltages or the link currents. For an RC tree all of the links (open capacitances) are current sources, and therefore, the solution for the link currents is trivial:

$$i_I = I. \tag{52}$$

The state variables, or link voltages, are then obtained

$$\boldsymbol{v}_{l} = -\boldsymbol{F}^{T}\boldsymbol{R}\boldsymbol{F}\boldsymbol{I} + \boldsymbol{F}^{T}\boldsymbol{V}_{s} \tag{53}$$

where R is a diagonal matrix of the tree branch resistances,  $V_s$  is a diagonal matrix of tree branch voltage sources, and I is the vector of link currents for this RC tree from (52). The matrix  $F^T RF$  does not involve multiplication but rather can be formed by inspection of the tree link graph, or F matrix, as described in [29], [30]. Equation (53) for this circuit is

$$\begin{bmatrix}

-R_1 \\

-R_1 \\

-(R_1 + R_3) \\

-(R_1 + R_3 + R_4)

\end{bmatrix}

\begin{bmatrix}

I_1 \\

I_2 \\

I_3 \\

I_4

\end{bmatrix}

-

\begin{bmatrix}

u(t) \\

u(t) \\

u(t) \\

u(t)

\end{bmatrix}.$$

(54)

The  $m_{-1}$  moment, or steady state, can be found from (54) by setting I equal to 0, and solving for the resulting explicit expression for  $v_l$ . If u(t) is a 5-V step input:

$$\boldsymbol{v}_l = \boldsymbol{v}_{ss} = -\boldsymbol{m}_{-1} \tag{55}$$

in this case a vector all entries of which are five. The  $m_0$ moment is obtained by setting I in (53) equal to  $Cv_{ss}$  and  $V_s$  equal to **0** and solving for  $v_l$  for all the nodes of interest. Solving  $v_l$  for all four state variables results in:

$$v_{l} = -\begin{bmatrix} -R_{1}(C_{1} + C_{2} + C_{3} + C_{4}) \\ -R_{1}(C_{1} + C_{2} + C_{3} + C_{4}) - R_{2}C_{2} \\ -R_{1}(C_{1} + C_{2} + C_{3} + C_{4}) - R_{3}(C_{3} + C_{4}) \\ -R_{1}(C_{1} + C_{2} + C_{3} + C_{4}) - R_{3}(C_{3} + C_{4}) - R_{4}C_{4} \end{bmatrix} = \begin{bmatrix} T_{D}^{1} \\ T_{D}^{2} \\ T_{D}^{3} \\ T_{D}^{4} \end{bmatrix}$$

(56)

which are the Elmore delays for the respective nodes. From (54) and (56) it is apparent that finding the Elmore delays via tree link analysis is also O(n), as is the case for a *tree walk*.

Once the first two moments  $m_{-1}$  ( $V_{ss}$ ) and  $m_0$  ( $T_D$ ) are determined, a first-order approximation can be made for the node voltages. The homogeneous response at node four is approximated by the first-order model

$$\hat{V}_4(s) = \frac{k_1}{(s-p_1)} = \frac{-k_1\tau_1}{(1-s\tau_1)}$$

$$= -k_1\tau_1(1+s\tau_1+s^2\tau_1^2+\cdots). \quad (57)$$

Equating the first two moments of this model to that of the actual circuit:

$$k_1 = [m_{-1}]_A = -5. (58)$$

and

$$-k_1 \tau_1 = \left[ m_{-1} \right]_4 = R_1 (C_1 + C_2 + C_3 + C_4)$$

$$+ R_3 (C_3 + C_4) + R_4 C_4. \tag{59}$$

The first-order AWE step response approximation for the voltage at  $C_4$  is

$$v_4 = v_{n4} + v_{h4} = 5 - 5e^{-t/\tau_1} \tag{60}$$

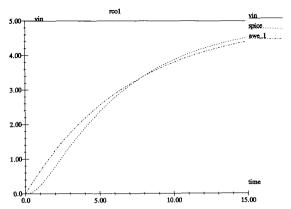

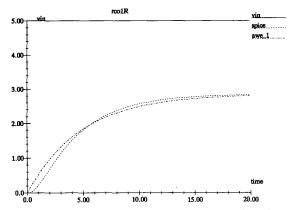

where  $\tau_1$  is equal to the Elmore delay. Equation (60) is compared with the SPICE response for this circuit in Fig. 7

We have shown that a first-order AWE analysis is equivalent to those RC tree methods that utilize Elmore's delay expression. In addition, solving for the  $m_0$  term at  $C_4$ , or  $T_D^4$ , by way of tree link analysis was shown to be equivalent to a tree walk as described in [7]. More importantly though, when the path is such that a walk is not possible, e.g., it may contain a floating capacitor, it will be shown that tree link analysis continues to apply without loss of generality.

## 4.2. Inexplicit Steady-State Solution

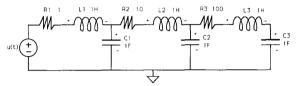

An explicit solution to the circuit with capacitors replaced by current sources and inductors replaced by voltage sources is also possible for circuit configurations other than RC trees. Any RLC circuit for which the tree can be specified by only inductors, or the links can be specified by only capacitors has a trivial dc solution. For instance, the RLC ladder shown in Fig. 8 can be solved explicitly since all of the links are capacitors.

There are cases, such as a resistor to ground with the RC tree in Fig. 9 which actually require obtaining the LU factors since the steady state is no longer explicit and the links are not exclusively capacitors. Irrespective of the method used to approximate the transient response waveform, the steady state must be determined a priori. Tree link analysis recognizes when the steady-state solution is not explicit and formulates the problem to solve for the least number of variables. With the capacitors replaced by current sources as shown in Fig. 11, the tree link graph

Fig. 7. First-order step response approximation for the *RC* tree circuit of Fig. 4.

Fig. 8. RLC Ladder which has a trivial steady-state solution.

Fig. 9. RC circuit example with grounded resistor.

for this circuit is now as shown in Fig. 10. The resistors form a cycle in the graph, hence, one of them, for this example,  $R_5$  (conductance  $G_5$ ), must be entered as a link.

The link currents can be found from the loop equations:

$$I_l = -GF^T RFi_l + I_s (61)$$

where G is the diagonal conductance matrix:

The first four link current expressions are again explicit, and the expression for  $I_{G5}$  can be obtained with a complexity of  $\mathcal{O}(n)$ . Thus calculation of the steady state and first moment with the inclusion of a grounded resistor is still linear in circuit size.

In Section II, the extension of *RC* tree methods to include the effects of grounded resistance were briefly discussed. Essentially the Elmore delay, or first moment, was

Fig. 10. Tree link graph for the circuit of Fig. 9 when the dc solution is not explicit.

Fig. 11. Capacitors replaced by current sources in the circuit of Fig. 9.

scaled by the steady-state voltage as described by (3). From (49) it is apparent that the first moment is changed not only by the change in steady state,  $v_{ss}(0)$ , as reflected by the change in  $x_h(0)$ , but also by the change in  $G^{-1}$ . With  $R_5 = 4 \Omega$ , the first-order AWE approximation is compared with the SPICE response in Fig. 12.

## 4.3. Finite Input Rise Time

Finite input signal voltage rise times can have a significant, even dominant impact on the overall response waveform. RC tree methods typically apply only to step response approximations. Finite input voltage slope effects have been considered by adding the input signal rise time to the Elmore delay to approximate the overall delay [31]. A more generalized approach for including input rise time effects is available with AWE.

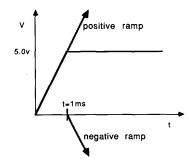

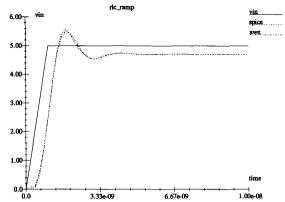

Consider the RC tree in Fig. 4 driven by a 5-V input signal with a rise time of 1 ms. Because the RC tree is linear, AWE can approximate this circuit response by superposing the results from positive- and negative-going ramp inputs as shown in Fig. 13. Only the positive ramp solution needs to be obtained since the negative ramp response has the same solution but is of oppositive sign and shifted in time by 1 ms.

The particular solution at node 4 for the positive-going ramp is

$$v_p(t) = 5 \times 10^3 t - 3.5 \times 10^4.$$

(63)

The first-order AWE approximation for the homogeneous solution at node 4 is

$$v_h(t) = 3.5e^{-1.667t}. (64)$$

The complete response approximation is the combined response from (63) and (64) for the positive and negative ramps.

Fig. 12. Response for RC tree with grounded resistor of Fig. 9.

Fig. 13. Superposition of two infinite ramps to form a "step with finite rise time."

$$v(t) = v_p(t) + v_h(t), \qquad 0 \le t \le 1mS \quad (65)$$

and

$$v(t) = v_p(t) + v_h(t) - v_p(t - 1 mS) - v_h(t - 1mS), \quad t \ge 1mS.$$

(66)

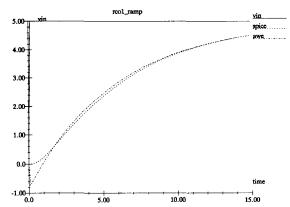

Equations (65) and (66) are shown plotted in comparison to the SPICE response in Fig. 14. The first-order AWE ramp response approximation makes a good prediction of the delay. The largest error in this waveform approximation occurs near time t = 0. This error is to be expected since the AWE approximation is matching the frequency expansion about  $s = 0 (t = \infty)$ . From Fig. 14 it is apparent that the AWE approximation starts out with a negative slope. In reality, this is not possible for an RC tree response when there are equilibrium initial conditions. The problem is that the initial boundary conditions for the case of a ramp input have not been met completely. For the case of a step response approximation the initial boundary conditions for the current as well as the voltage are met by matching the  $m_{-1}$  term. To ensure that the same is true for a ramp input both the  $m_{-1}$  and the  $m_{-2}$ terms must be matched. Matching the  $m_{-2}$  term is tantamount to ensuring that the first derivative of the approximate voltage response matches the first derivative of the actual voltage response at time t = 0. This extended matching guarantees that the initial slope at time t = 0 is

Fig. 14. First-order AWE approximation of ramp response for the circuit of Fig. 4.

of the correct sign. For most timing analysis applications the possible error in voltage slope at time t=0 does not affect the delay estimate. However, if necessary, this glitch can be removed by proper matching of the  $m_{-2}$  terms. Moreover, as more positive moments are matched, i.e., the order of approximation is increased, the initial slope at t=0 better approaches exact. This phenomenon will be demonstrated by several ramp response examples in the next section.

## 4.4. Increased Orders of Approximation

The first-order step response approximation in Fig. 7 exhibits an error which may be unacceptable for some delay applications. In [7], what corresponds to a first-order AWE response waveform is bounded to what are sometimes overly pessimistic max/min values. Since with AWE higher orders of approximation can be obtained at an incremental cost to the first-order approximation, the order of approximation is increased until an acceptable error term exists. For the first-order approximation, the error term as described in Section III-3.4, is calculated to be 36 percent. A second-order approximation for the RC tree in Fig. 4 can be obtained upon calculating the next two moments. The second-order AWE unit step response approximation is compared with the SPICE response in Fig. 15. The error term is decreased to 1.6 percent. The AWE and SPICE response plots are indistinguishable at the resolution shown. Higher orders of approximation are obviously desirable for improving the accuracy of the response approximation. More importantly, though, higher orders of approximation are necessary for the general handling of nonmonotone response waveforms arising from circuits which contain multiple input signals, nonequilibrium initial conditions, floating capacitors, complex poles, ect. In the section which follows several examples are used to demonstrate AWE's ability to analyze these types of circuit responses.

# V. GENERAL RLC CIRCUIT EXAMPLES

A first-order AWE approximation has been shown to be equivalent to some of the RC tree methods. The benefit

Fig. 15. Second-order step response approximation for the circuit of Fig. 4.

of AWE is the ability to recognize and handle more complex interconnect models without loss of generality. In this section some linear RLC circuits are used to demonstrate the applicability of AWE for solving general linear interconnect models.

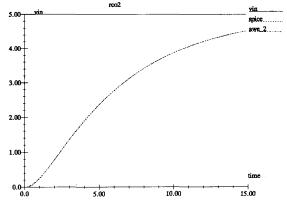

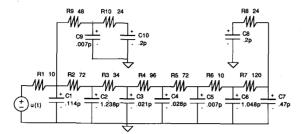

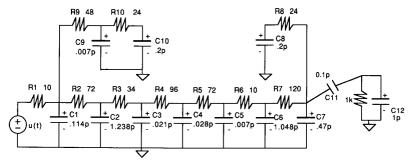

#### 5.1. MOS Interconnect

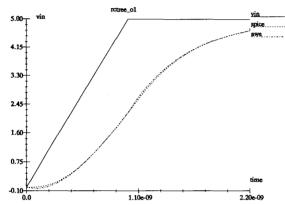

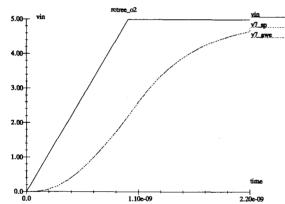

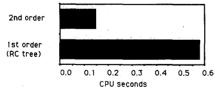

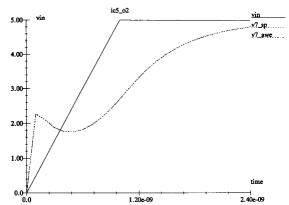

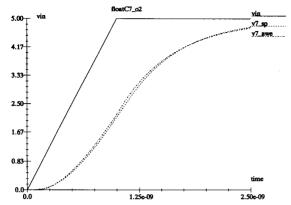

Low- to mid-frequency MOS circuit interconnect can be modeled well with an RC tree. The RC tree in Fig. 16 is a typical example of such a model. Of particular interest is the widely varying time constants for this circuit. Stiff circuits such as this RC tree are normally troublesome for circuit [8] and timing [32], [33] simulators; however, in AWE the small time constants are not obtained if they are not required for the delay estimation. For the case of no initial nonzero voltages and a positive input with a slope of 1 ns, the first-order AWE approximation for the voltage across  $C_7$  is shown and compared with that of SPICE in Fig. 17. The error term (from Section III-3.4) is calculated to be 4.4 percent. A second-order approximation is made by determining the next two moments. The second-order approximation is shown in Fig. 18. At the resolution shown, this approximation and the SPICE response are difficult to distinguish. The error term is decreased to 0.15 percent.

Higher orders of approximation not only provide an improved waveform estimate but also enables a measure of the accuracy of the first-order approximation. This capability is essential for interconnect models in general, since there may be complex poles or low frequency zeros which render a first-order approximation useless. Moreover, as described in Sections III and IV, the higher orders of approximation are obtained at an incremental cost to the firstorder estimate. For example, the cost of a second-order approximation as compared to the first-order estimate for this circuit is shown in Fig. 19. The first-order approximation time is the CPU time required to set up the equations, find the steady state and  $m_0$ , and solve for the dominant pole and residue. The second-order approximation incremental CPU time is that required to find the next two moments, and the two approximating poles and residues.

Fig. 16. RC tree with widely varying time constants.

Fig. 17. First-order approximation for the voltage at capacitor  $C_7$  in the circuit of Fig. 16.

Fig. 18. Second-order approximation for the voltage at capacitor  $C_7$  in the circuit of Fig. 16.

Fig. 19. CPU time comparison between first- and second-order approximation for the circuit of Fig. 16.

The approximate poles for the first- and second-order approximations are given along with the actual poles in Table I. The first-order AWE analysis approximates the dominant pole at a value very close to the actual dominant

TABLE I

Approximating and Exact Poles for RC Tree Example

|            | ))=5.0 v   | $V_{c6}(t=0)$ | no initial conditions |           |

|------------|------------|---------------|-----------------------|-----------|

| actual     | 2nd order  | 1st order     | 2nd order             | 1st order |

| -1.7818e9  | -1.7818e9  | -9.6949e8     | -1.7818e9             | 1.7358e9  |

| -1.3830e10 | -2.6920e10 |               | -1.2572e10            |           |

| -2.5679e10 |            |               |                       |           |

| -6.0618e10 | -          |               |                       |           |

| -2.4933e11 |            |               |                       |           |

| -6.6997ell |            |               |                       |           |

| -1.1236e12 |            |               |                       |           |

| -9.1359e12 |            |               |                       |           |

| -2.0599e12 |            |               |                       |           |

| -1.6417e13 |            |               |                       |           |

pole. The second-order approximation finds two poles very close to the first two actual poles. In general, as the order of the approximation is increased, the approximate poles are found to "creep up on" the actual circuit poles as demonstrated by this example.

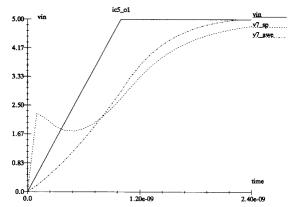

## 5.2. Nonequilibrium Initial Conditions

With AWE arbitrary nonequilibrium initial conditions and charge sharing are handled for general RLC circuits. The initial state of the circuit may cause charge to be shared between capacitors which can affect the delay at various nodes. It is well known that the initial state of a circuit,  $x_0$ , can excite or suppress various of its natural frequencies [28]. With AWE the moments are functions of the initial conditions  $x_0$  so as to include this effect. The dominant pole approximations are, therefore, determined by the initial state as well as the circuit elements. With the initial voltage of C<sub>6</sub> in Fig. 16 equal to 5 V, the firstand second-order approximate poles that result are shown in Table I. The AWE approximation for the case of  $v_6(t)$ = 0) = 0 shows the two most dominant poles to be very near the first two actual poles. With  $v_6(t=0) = 5$ , however, the initial conditions introduce a low-frequency zero which partially cancels the second pole. The AWE approximation finds the two most dominant poles to be near the first and third actual poles when  $v_6(t=0)=5$ . The first- and second-order approximate waveforms determined by these approximate poles are shown in Figs. 20 and 21, respectively. Obviously, a first-order approximation, or single exponential function, cannot be used to approximate this nonmonotone response. The error term for this first-order approximation is 150 percent. The second-order AWE response, which has an error estimate of 0.65 percent, is indistinguishable from the SPICE response at the resolution of this plot.

# 5.3. Floating Capacitors

Although floating capacitors do not usually appear in digital signal paths directly, the charge that may be dumped to other paths due to coupling capacitance cannot always be neglected. In MOS technologies the floating capacitors which model the gate-drain can sometimes significantly affect the delay. For example, consider the RC tree circuit in Fig. 16 with a floating capacitor connected

Fig. 20. First-order approximation for the response of the circuit in Fig. 16 with  $v_{cb}(0) = 5.0$ .

Fig. 21. Second-order approximation for the response of the circuit in Fig. 16 with  $v_{c6}(0)=5.0$ .

Fig. 22. RC tree of Fig. 16 with a floating capacitor added.

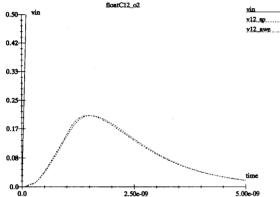

to the output node as shown in Fig. 22. The second-order approximation for the voltage at  $C_7$  is shown in Fig. 23. The delay, taken to be the point at which a logic threshold of 4.0 V is reached, changes from 1.6 to 1.7 ns because of charge sharing through  $C_{11}$  to  $C_{12}$ . Notice too, that this second-order approximation is not as accurate as the response approximation in Fig. 18. This inaccuracy is reflected in the error term which is now 15 percent with the floating capacitance path, as compared to 0.15 percent without it. From second- to third-order the error term reduces from 15 to 0.14 percent.

The charge dumped onto  $C_{12}$  is shown in Fig. 24. Note that since we match the  $m_0$  term of the actual response, the area under these voltage curves, hence, the charge transferred, is always exact.

## 5.4. Inductors

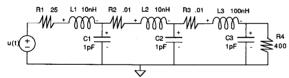

For an example of a circuit with complex poles consider the analysis of the underdamped RLC circuit in Fig. 25. This circuit is characterized by three pairs of complex poles as shown in Table II. A first-order AWE approximation for a circuit with dominant complex poles pro-

Fig. 23. Second-order approximation for the voltage of capacitor  $C_7$  in the circuit of Fig. 22.

Fig. 24. Second-order approximation for the voltage of capacitor  $C_{12}$  in the circuit of Fig. 22.

Fig. 25. RLC underdamped circuit with complex dominant poles.

TABLE II

RLC CIRCUIT POLES AND APPROXIMATE POLES

| 2nd order |            | 4th       | order      | A         | ctual       |

|-----------|------------|-----------|------------|-----------|-------------|

| -1.0881e9 | -2.6125e9j | -1.3532e9 | -2.5967e9j | -1.3532e9 | -2.5967e9j  |

| -1.0881e9 | +2.6125e9j | -1.3532e9 | +2.5967e9j | -1.3532e9 | +2.5967e9j  |

|           |            | -7.3532e8 | -6.7541e9j | -8.194e8  | -6.810e9j   |

|           |            | -7.3532e8 | +6.7541e9j | -8.194e8  | +6.810e9j   |

|           |            |           |            | -3.278e8  | +1.6225e10j |

|           |            | *         |            | -3.278e8  | -1.6225e10j |

duces inaccurate results. The nonmonotone homogeneous response cannot be modeled by a single exponential function. A second-order approximation is required minimally.

The input voltage is a 5-V ideal step. A first-order approximation produces a single real dominant pole at p =

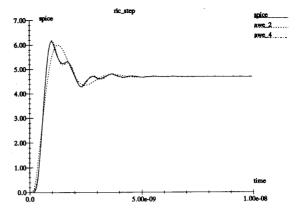

Fig. 26. AWE second- and fourth-order approximations for the step response of the *RLC* circuit in Fig. 25.

-2.833e9. The error term for this first-order approximation is large-74 percent. A second-order AWE analysis yields the approximating poles shown in Table II. This dominant complex pole pair is near the actual first pole pair shown in Table II. The second-order AWE approximation is compared with the SPICE response in Fig. 26. At second-order, AWE is able to detect the overshoot but there is still a significant waveform difference as compared to the SPICE response. The error term at second order is 22 percent. It is only at fourth order, with the approximating poles shown in Table II, that the error term becomes less than 1 percent and all of the response waveform detail is matched. The fourth-order AWE response is also shown plotted in Fig. 26. For the most part, this approximation is coincident with the SPICE waveform plot.

The step response at  $C_3$  was shown to be dominated by two pairs of complex poles. The residues were such that both pairs of poles made significant contributions to the response waveform. If the input voltage rise time were changed from 0 to 1 ns, the residues would be changed such that there would be only one complex pole pair dominating the response. The second-order RLC circuit response to a 5-V input with a 1-ns rise time is compared to the corresponding SPICE response in Fig. 27. As in the RC tree case, the rise time of the input signal affects the error of the approximation. In general, the step response approximation will exhibit the largest error term since its transient response is more significant than for the case of finite input signal slope.

# VI. Conclusions

AWE is an efficient approach to waveform estimation for linear *RLC* interconnect circuit models. Floating capacitors, inductors, linear controlled sources, finite input rise time, and charge sharing are all easily addressed in terms of AWE at any level of detail by merely increasing the order of the approximation. Because of its generality AWE should be applicable both to bipolar circuitry and printed circuit board level interconnect as well as to MOS circuit and interconnect timing estimation.

Fig. 27. AWE second-order approximation for the RLC circuit in Fig. 25 with a 1-nS/input voltage rise time.

#### ACKNOWLEDGMENT

The authors wish to thank especially Xiaoli Huang, Dominic Virgilio, and Krishnan Ravichandran from CMU for their contributions to Asymptotic Waveform Evaluation. They would also like to thank John Wyatt, Bruce Krogh, Steve McCormick, Jonathan Allen, and Stephen Haley for the helpful discussions they had with them during the course of this work.

## REFERENCES

- [1] J. K. Ousterhout, "CRYSTAL: A timing analyzer for NMOS VLSI circuits," in Proc. 3rd Caltech Conf. on VLSI, pp. 57-69, Mar. 1983:

- -, "Switch-level delay models for digital MOS VLSI," in Proc.

- 21st Design Automation Conf., pp. 542-548, 1984.

[3] N. P. Jouppi, "TV: An nMOS timing analyzer," in Proc. 3rd CalTech Conf. on VLSI, Mar. 1983.

- -, "Timing analysis and performance improvement of MOS VLSI IEEE Trans. Computer-Aided Design, vol. CAD-6, pp. designs,' 650-665, 1987.

- [5] T.-M. Lin and C. A. Mead, "Signal delay in general RC networks," IEEE Trans. Computer-Aided Design, vol. CAD-3, pp. 331-349,

- [6] C. J. Terman, "Simulation tools for digital LSI design," Ph.D. dissertation, Massachusetts Institute of Technology, Sept. 1983.

- [7] P. Penfield and J. Rubenstein, "Signal delay in RC tree networks," in Proc. 19th Design Automation Conf., pp. 613-617, 1981.

- [8] L. W. Nagel, "SPICE2, A computer program to simulate semiconductor circuits," Tech. Rep. ERL-M520, Univ. Calif., Berkeley, May

- W. C. Elmore, "The transient response of damped linear networks with particular regard to wideband amplifiers," J. Appl. Phys., vol. 19, no. 1, pp. 55-63, 1948.

- [10] P. O'Brien and J. Wyatt, "Signal delay in ECL interconnect," in Proc. IEEE Int. Symp. on Circuits and Systems, May 1986.

- [11] J. L. Wyatt, "Signal propagation delay in RC models for interconnect" in Circuit Analysis, Simulation and Design. Amsterdam, The

- Netherlands: North-Holland, 1987. C. Chu and M. Horowitz, "Charge-sharing models for switch-level Simulation," IEEE Trans. Computer-Aided Design, vol. 6, pp. 1053-1060, 1987,

- [13] R. E. Bryant, "MOSSIM: A switch level simulator for MOS LSI." in Proc. 18th Design Automation Conf., June 1981.

- [14] J. Rubenstein, P. Penfield, Jr., and M. A. Horowitz," Signal delay in RC tree networks," IEEE Trans. Computer-Aided Design, vol. CAD-2, pp. 202-211, 1983.

- [15] A. Raghunathan and C. D. Thompson, "Signal delays in RC trees with charge sharing and leakage," in Proc. 19th Asilomar Conf. on Circuits, Systems and Computers, Nov. 1985.

- [16] C. Shi and K. Zhang, "A robust approach for timing verification," in Proc. Int. Conf. on Computer-Aided Design, Nov. 1987.

- [17] M. A. Horowitz, "Timing models for MOS circuits," Ph.D. dissertation, Stanford Univ., Jan. 1984.

- L. O. Chua and P. Lin, Computer-Aided Analysis of Electronic Circuits: Algorithms and Computational Techniques. Englewood Cliffs. NJ: Prentice-Hall, 1975

- [19] J. Vlach and K. Singhal, Computer Methods for Circuit Analysis and Design. New York: Van Nostrand Reinhold, 1983.

- [20] A. Ralston and P. Ratinowitz, First Course in Numerical Analysis. New York: McGraw-Hill, 1978.

- [21] C. G. Cullen, Linear Algebra and Differential Equations. Boston, MA: Prindle, Weber and Schmidt, 1980.

- [22] L. T. Pillage, "Asymptotic waveform evaluation for timing analysis," Ph.D. dissertation, Carnegie Mellon Univ., Apr. 1989

- [23] M. Lal and R. Mitra, "Simplification of large system dynamics using a moment evaluation algorithm," IEEE Trans. Auto. Cont., vol. pp. 602-603, Oct. 1974.

- [24] F. Ba Hli, "A general method for time domain synthesis," Trans. IRE, pp. 21-29, Sept. 1954.

- [25] W. H. Kautz, "Transient synthesis in the time domain," Trans. IRE, pp. 29-39, Sept. 1954.

- V. Zakian, "Simplification of linear time-invariant systems by moment approximants," Int. J. Cont., vol. 18, pp. 455-460, 1973

- D. S. Mitrinovic, Analytic Inequalities. New York: Springer-Verlag, 1970.

- [28] C. Desoer and E. Kuh, Basic Circuit Theory. New York: McGraw-Hill, 1969.

- [29] L. T. Pillage, H. Xiaoli, and R. A. Rohrer, "Tree/link partitioning for the implicit solution of circuits," in *Proc. Int. Symp. on Circuits* and Systems, May 1987.

- [30] H. Xiaoli, L. T. Pillage, and R. A. Rohrer, "TALISMAN: A piecewise linear simulator based on tree/link repartitioning," in Proc. Int. Conf. on Computer-Aided Design, Nov. 1987.

- [31] M. A. Cirit, "RC trees revisited," in Proc. Custom Integrated Circuits Conf., May 1988.

- [32] Y. H. Kim, J. E. Kleckner, R. A. Saleh, and A. R. Newton, "Electrical-logic simulation," in Dig. 1984 Int. Conf. on Computer-Aided Design, pp. 7-10, Nov. 1984.

- C. Visweswariah and R. A. Rohrer, "SPECS2: An integrated circuit timing simulator," in Proc. Int. Conf. on Computer-Aided Design, Nov. 1987.

- [34] L. Pillage, X. Huang, and R. Rohrer, "AWEsim: Asymptotic wave-form evaluation for timing analysis," in *Proc. 26th Design Automa*tion Conf., 1989.

VLSI design and test.

Lawrence T. Pillage received the B.S.E.E. and the M.S.E.E. degrees from the University of Pittsburgh, and the Ph.D. degree in electrical and computer engineering from Carnegie Mellon University, in 1983, 1985, and 1989, respectively.

He worked for Westinghouse Research and Development for two years where he acquired three patents. He is currently an Assistant Professor of electrical and computer engineering at the University of Texas at Austin. His research interests include circuit and timing simulation and

His early work in circuit simulation formed the basis for the development of the SPICE family of circuit simulators, circuit simulation, and automatic nonlinear circuit synthesis. He is the founding editor of the IEEE TRANSACTIONS ON COM-PUTER-AIDED DESIGN and the author and co-author

of three textbooks and several papers. He is currently a Professor of electrical and computer engineering at Carnegie Mellon University, Pittsburgh,

Dr. Rohrer was the President of the IEEE Circuits and Systems Society in 1987. He has received several engineering awards and in 1989 was elected to the National Academy of Engineering.