# Determination of Worst-Case Crosstalk Noise for Non-Switching Victims in GHz+ Buses

Jun Chen ECE Department University of Wisconsin, Madison junc@cae.wisc.edu

# ABSTRACT

Considering RLC interconnect model and multiple switching aggressors, we study switching pattern generation and switching time alignment that leads to worst-case crosstalk noise for a quiet victim or a noisy one. We assume that aggressors can have arbitrary switching patterns and can switch at arbitrary times. We show that the commonly used superposition algorithm results in 15% underestimation on average, and propose a new algorithm that has virtually the same complexity as the superposition algorithm but approximates the exhaustive search very well with only 4% underestimation on average. Further, we show that applying RC model to GHz+ interconnects in IRTS  $0.10\mu m$  technology underestimates crosstalk noise by up to 80%, and convincingly conclude that RLC model is necessary to analyze such interconnects.

# **Categories and Subject Descriptors**

B.7.2 [Integrated Circuits]: Design Aids—Verification

#### **General Terms**

Design, Performance, Theory, Verification

#### Keywords

Interconnect Design

# 1. INTRODUCTION

Coupling induced crosstalk noise gains growing importance in deep-submicron circuits and systems. The worstcase noise (WCN) defined as the maximum crosstalk noise peak has been studied in [1]. It is assumed that driver and receiver sizes, wire spacings, and net ordering are given, and interconnects can be modeled by distributed RC circuits. Then, the WCN problem is formulated as the alignment of switching times for multiple aggressors such that WCN is induced.

Copyright 2002 ACM 1-58113-526-2/02/0012 ...\$5.00.

Lei He EE Department University of Californa, Los Angeles Ihe@ee.ucla.edu

As we move to GHz+ designs, the inductive crosstalk noise can no longer be ignored [2]. The WCN problem becomes much more complicated under RLC interconnect models. We need to consider (i) switching pattern generation in addition to alignment of switching times for multiple aggressors, as the same direction switching assumed for the WCN problem under RC model does *not* always lead to WCN under RLC model; and (ii) coupling between both adjacent and non-adjacent interconnects, meanwhile the WCN problem under RC model only takes into account coupling between adjacent interconnects.

Considering RLC interconnect model and multiple switching aggressors, we study in this paper the switching pattern generation and switching time alignment problem resulting in WCN at the far-end of a quiet victim or a noisy one. The rest of the paper is organized as follows: In section 2, we review the WCN problem formulation and algorithms under RC model in detail. In section 3, we formulate and solve the WCN problem under RLC model. We present experiments in section 4, and conclude in section 5.

# 2. PRELIMINARIES AND REVIEW

### 2.1 Interconnect and device models

We study the interconnect bus structure with one victim wire (in short, the victim) and multiple aggressor wires (in short, the aggressors). A victim is *quiet* when there is no signal/noise propagated from its previous stage, it is *noisy* when the signal/noise propagated from the previous stage is less than the logic threshold, and it is *switching* otherwise. In this paper, we study WCN only for non-switching victims that are either quiet or noisy. Moreover, we assume that aggressors may have arbitrary switching patterns (i.e., switching high or switching low), and may switch at arbitrary moments.

We assume that all drivers (receivers) have a uniform size, and all drivers and receivers are cascade inverters. For best accuracy, we use the BSIM model[4] for the predicted ITRS  $0.10\mu m$  technology to model all drivers and receivers. The BSIM model is a nonlinear device model. In contrast, there are linearized device models, such as the effective switching resistance model [5] and  $C_{eff}$  model [6]. The effective switching resistance model uses a fixed-value resistor to model a device. Interconnects with drivers and receivers become linear circuits under this model, leading to inaccurate estimation of WCN.<sup>1</sup> The  $C_{eff}$  model is able to catch the device nonlinearity for a single RC or RLC tree, and has

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

TAU'02, December 2–3, 2002, Monterey, California, USA.

<sup>&</sup>lt;sup>1</sup>Superposition achieves the accurate solution only for a lin-

been used for the worst-case delay problem under RC models [7]. We plan to study its applicability to the WCN problem under RLC model in the future but not in this work.

Interconnects can be modeled by either RC or RLC circuits. In this work, we assume that all wires have a uniform width and spacing, and construct a  $\pi$ -type circuit for every  $200\mu m$  long wire segment for both RC and RLC models. We only consider the coupling capacitance between adjacent wires because coupling capacitance between nonadjacent wires is negligible. For RC models, both self inductance and mutual inductance are ignored. For RLC models, we consider self inductance for each wire segment, and mutual inductance between a pair of any two wire segments, even though they may belong to the same net. Such an RLC circuit model is called a full model in [8]. The full model is accurate and is applicable to either aligned or unaligned buses to be studied in this paper. It has been shown that for aligned buses, a normalized model with a much reduced complexity may achieve a similar accuracy when compared to the full model [8, 9]. Therefore, we use the normalized model for aligned buses, and the full model for unaligned buses.

We use SPICE simulation of the resulting RLC circuits with nonlinear drivers and receivers to validate our WCN algorithms to be presented in this paper. In the following of this paper, we use the predicted ITRS  $0.10\mu$ m technology (see table 1). We assume that the input rising time is 33ps, which is 10% of the clock period of the predicted 3GHz clock. We assume uniform receiver size and driver size. We measure noise at the inputs of receivers and and report noise normalized with respect to VDD. It is worthwhile to point out that our algorithms can be applied to any accurate interconnect analysis methods.

| Technology         | ITRS $0.10\mu m$ |

|--------------------|------------------|

| Signal rising time | 33 ps            |

| Wire length        | $1000 \mu m$     |

| Wire thichness     | $0.75 \mu m$     |

| Wire width         | $0.6 \mu { m m}$ |

| Driver size        | 30x to $200x$    |

| Receiver size      | 10x              |

Table 1: Experiment settings

# 2.2 WCN under RC model

If only capacitive coupling is considered, there is no resonance in the noise waveform. When one aggressor switches, there is only one noise peak on the victim with the polarity same as that of the aggressor. For the sake of WCN, all the noise peaks should have a same polarity, and so do all the aggressor signals. Therefore, the WCN problem under RC model can be simplified as the alignment problem of aggressor switching times to maximize the resulting noise in the victim, without considering aggressor switching patterns.

The following algorithms have been proposed for the WCN problem under RC model in [1]:

• *Exhaustive searching* (**ES**): Explicitly search the entire solution space. WCN is defined as the maximum noise value found during this process.

- Simultaneous switching (**SS**): All the aggressors switch simultaneously. WCN is approximated by the maximum noise value on the victim.

- Superposition (SP): Find the maximum noise peak when only one aggressor switches, then approximate WCN by the sum of all such noise peaks.

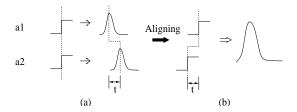

- Aligned Switching (AS): Find the peak time as the time of the maximum noise peak when only one aggressor switches, then simulate the interconnect structure with all aggressors switching at the times *aligned* according to the above peak times (see an alignment example in fig.1). The resulting maximum noise in the last simulation is WCN.

Figure 1: Alignment operation illustrated using two aggressors. (a) We simulate the interconnects with only one aggressor switching in each simulation, and find the skew t between noise peaks. (b) We simulate the interconnects with both aggressors switching. When their switching times are aligned by t, the overall noise due to the two aggressors is likely maximized [1].

The (**ES**) method has a time complexity of  $O(m^n)$ , where m is the total searching steps for one aggressor and n is the total number of aggressors. In contrast, the time complexity is 1 for **SS**, n for **SP**, and n + 1 for **AS**. Here, we measure complexity in terms of the total number of simulations needed to analyze the interconnect structure. According to [1], **AS** closely approximates WCN with underestimation less than 5%, **SS** always underestimates the WCN, and **SP** can severely overestimate or underestimate the WCN. We will discuss how to extend **ES**, **SS**, **SP** and **AS** for the WCN problem under RLC model in section 3.

# 3. WCN UNDER RLC MODEL

# 3.1 **Problem Formulation**

#### 3.1.1 Impact of Shielding

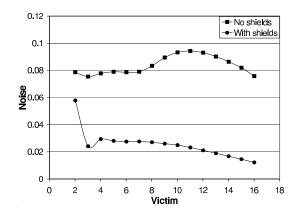

In this work, we assume there are shields at both edges of the bus structure under study. This assumption is realistic, because there are always power/ground wires in the same or adjacent routing layer and these wires can serve as shield wires. Further, a few recent papers [10, 11, 12] have proposed to insert dedicated shields to further reduce crosstalk noise. We have studied noise in a sixteen-bit bus structure with and without edge shields. We assume that bit-1 is the aggressor, and compute noise for quiet victims from bit-2 to bit-16 (see fig.2). One can easily see the noise is much smaller with presence of edge shielding wires.

ear circuit. Because the devices are not linear in nature, our experiments in section 4 will show that superposition leads to underestimation in most cases.

Figure 2: Noise in a sixteen-bit  $1000\mu$ m-long bus. The driver size is  $200\times$ , and the wire spacing is  $0.6\mu$ m

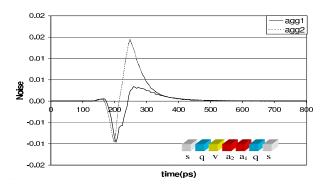

Figure 3: noises on the victim caused by two aggressors in a five-bit  $1000\mu m$ -long bus. The driver size is  $30\times$ , and the wire spacing is  $1.7\mu m$ .

#### 3.1.2 Impact of Switching Pattern

Different from the RC interconnect model, there may be resonance in the waveform due to inductance under the RLC model. Resonance results in multiple noise peaks with opposite polarities. It is not certain which peak is the largest. In fig.3, we show a bus structure with two aggressors, where **v** is the quiet victim, **q** is a quiet wire, **a** is an aggressor, and  $\mathbf{s}$  is a shield. We also present two waveforms, each for the noise on the quiet victim with only one of the two aggressors switching up. Either the positive or negative peak in this example can be the larger one between the two peaks due to a same aggressor (in general, an aggressor may generate more than two noise peaks). Further, WCN may happen when aggressors switch in the same direction or different directions. Such an example is shown in table 2 for a same bus topology but with different wire spacings. Therefore, we must consider switching pattern generation in addition to switching time alignment for WCN under RLC models.

| bus   | driver      | spacing(um) | $noise1(\uparrow\uparrow)$ | $noise2(\uparrow\downarrow)$ |

|-------|-------------|-------------|----------------------------|------------------------------|

| svaas | $30 \times$ | 0.6         | 0.1323                     | 0.1006                       |

| svaas | $30 \times$ | 1.6         | 0.0197                     | 0.0229                       |

Table 2: Noise peaks for a three-bit  $1000\mu$ m-long bus structure. There are two aggressors whose switching patterns are shown inside the parentheses in the last two columns

### 3.1.3 WCN under RLC Interconnect Model

In summary, we define the WCN problem under RLC models as follows:

Given a non-switching victim and multiple aggressors, find switching patterns and switching times for all aggressors such that the resulting noise in the victim has a maximal amplitude.

#### Table 3: WCN problem under RLC model

Below, we discuss algorithms for quiet and noisy victims respectively.

# **3.2** Algorithms for Quiet Victim

## 3.2.1 Extension to Existing Algorithms

We extend SS, SP and AS by incorporating switching pattern generation as follows:

- Simultaneous switching (**SS**): All aggressors switch simultaneously in the same direction. WCN is approximated by the maximum noise in the victim.

- Superposition(**SP**): Find the maximum noise peak for each aggressor when only this aggressor switches. WCN is approximated by the sum of *amplitude* (absolute value) of all such peaks.

- Aligned switching(AS): Obtain individual noise waveforms by simulating the interconnect structure with only one aggressor switching each time, then simulate the interconnect structure with multiple aggressors using the following switching times and patterns:

- 1. align the maximum positive peaks of individual noise waveforms, and all aggressors switch in the same direction;

- 2. align the maximum negative peaks of individual noise waveforms, and all aggressors switch in the same direction;

- 3. align the peaks of maximum amplitude, and aggressors have switching directions such that all the aligned peaks have the same polarity.

WCN is approximated by the maximum noise among the above three simulations. Experiments have shown that none of the three kinds of alignments defined above is always better than the others, so all the three alignments are needed by the **AS** algorithm.

#### 3.2.2 New Algorithms

We first propose the following SS+AS algorithm. In SS+AS, WCN is approximated by the larger one between the results obtained by SS and AS. Experiments in section 4 will show that SS or AS alone can still lead to large underestimation. Also, neither of them is always better than the other. However, SS+AS is a good approximation to WCN under RLC models.

To measure the performance of different algorithms, we need a reasonably accurate solutions as a basis for comparison. Obviously exhaustive searching can provide accurate solution, but it is very time consuming, if not impossible for a large interconnect structure. Therefore, we develop the following pseudo exhaustive searching (**PES**) algorithm based on improvement of the **SS+AS** algorithm. We first obtain four initial solutions from **SS+AS**. For each initial solution, we keep its switching pattern and perform a branchand-bound procedure to improve the switching times for all aggressors. Within the framework of branch-and-bound for multiple aggressors, we apply the binary search to find the best switching time for a specific aggressor  $a_i$ . If the switching time is  $t_i$  for  $a_i$  in the initial solution, the initial solution space for the binary search is given by  $\{t_i - \Delta t, t_i + \Delta t\}$  where  $\Delta t$  is a preset constant of 25ps. WCN is the largest noise obtained by the **PES** algorithm.

#### *3.2.3 Time Complexity*

In table 4, we compare the time complexity for different WCN algorithms under the RLC model. In this table n is the number of aggressors, and m is the total time steps for one aggressor. **PES** has an exponential complexity, whereas **SS**, **SP**, **AS** and **SS**+**AS** all have a linear time complexity.

| Algorithm     | Aggressor alignment         | Time         |

|---------------|-----------------------------|--------------|

|               |                             | complexicity |

| SS            | simultaneous switching      | 1            |

| $\mathbf{SP}$ | sum of noise amplitude      | n            |

| AS            | align three type of noise   | n+3          |

|               | peaks                       |              |

| SS+AS         | simultaneous, align three   | n+4          |

|               | type of noise peaks         |              |

| PES           | pseudo exhaustive searching | $O(m^n)$     |

Table 4: Time complexity of WCN algorithms for quiet victims.

### 3.3 Algorithms for Noisy Victim

In this section we consider noisy victims with noise propagated from previous stages. We extend **SS**, **SP** and **AS** algorithms as follows:

- Simultaneous Switching(**SS**): We first find the time of maximum noise peak with all aggressors switching in the same direction simultaneously and assuming that the victim is quiet, and find the time of the maximum peak of the propagated noise. We then simulate the interconnects with all the aggressors switching in the same direction simultaneously, with aggressors aligned according to the above two times and the aggressors' peak noise having the same polarity as the propagated noise. WCN is approximated by the maximum noise in the last simulation.

- Superposition (SP): We first find the peak noise value when only one aggressor switches and the victim is quiet. WCN is approximated by the sum of all such peak noise values and the peak value of the propagated noise.

- Aligned Switching (AS): We first obtain individual noise waveform when only one aggressor switches, then carry out simulations with the three types of alignments defined in section 3.2 by treating the propagated

noise as an individual noise waveform of an "extra" aggressor. WCN is approximated by the maximum noise among the three alignment procedures.

The **SS+AS** and **PES** for noisy victims can be easily extended using the above **SS** and **AS** algorithms. Note in **PES** for noisy victims we need one more dimension for the propagated noise.

In table 5, we summarize the time complexity for algorithms with noisy victims. It is easy to see that the time complexity is almost the same as that of the corresponding algorithms for quiet victims.

| Algorithm | Aggressor alignment         | Time                     |

|-----------|-----------------------------|--------------------------|

|           |                             | complexicity             |

| SS        | simultaneous switching      | 3                        |

| SP        | sum of noise amplitude      | n+1                      |

| AS        | align three type of noise   | n+4                      |

|           | peaks                       |                          |

| SS+AS     | simultaneous, align three   | n+5                      |

|           | type of noise peaks         |                          |

| PES       | pseudo exhaustive searching | $\mathcal{O}(m^{(n+1)})$ |

Table 5: Time complexity of WCN algorithms for noisy victims.

# 4. EXPERIMENTS

In this section we present the experimental comparison between the algorithms presented in section 3.

## 4.1 Quiet Victim

## 4.1.1 Aligned Bus

Figure 4: Six-bit aligned bus with two shields

In this section we study the aligned six-bit coplanar bus structure as shown in fig.4. We present the simulation results for different algorithms in table 6. As shown in this table, **SS** and **AS** have average underestimation less then 5% and the maximum underestimation is about 10% compared to **PES**. **SS+AS** gives results very close to **PES**. Maximum underestimation of **SS+AS** is about 5% and average underestimation is less than 3%. **SP** can underestimate up to 24% compared to **PES**. WCN under RC model severely underestimate the noise in most cases, especially for strong drivers and larger spacing. The underestimation of applying RC model can be up to 80% compared to **PES**.

#### 4.1.2 Unaligned Bus

In this section we conduct experiments using unaligned bus structures. Although shifting between aggressors in an unaligned bus structure can affect the timing of each aggressor, such impact is not significant due to the short flight time for on-chip interconnects. To show the effect, we calculate the flight time in a 1000 $\mu$ m long wire. We assume the dielectric is uniform, the relative dielectric constant is  $\epsilon=1.9$ , and the relative permeability is  $\mu \approx 1$ . The speed

| Driver       | Spacing  | PES   | RC WCN  | SS     | SP      | AS      | SS+AS  |

|--------------|----------|-------|---------|--------|---------|---------|--------|

| $30 \times$  | 0.6      | 0.147 | 0.144   | 0.145  | 0.111   | 0.141   | 0.145  |

| $30 \times$  | 1.2      | 0.069 | 0.062   | 0.068  | 0.062   | 0.066   | 0.068  |

| $50 \times$  | 0.6      | 0.168 | 0.144   | 0.167  | 0.133   | 0.148   | 0.167  |

| $50 \times$  | 1.2      | 0.089 | 0.064   | 0.087  | 0.082   | 0.085   | 0.087  |

| $100 \times$ | 0.6      | 0.152 | 0.117   | 0.149  | 0.119   | 0.146   | 0.149  |

| $100 \times$ | 1.2      | 0.114 | 0.050   | 0.108  | 0.097   | 0.106   | 0.108  |

| $150 \times$ | 0.6      | 0.149 | 0.101   | 0.143  | 0.114   | 0.143   | 0.143  |

| $150 \times$ | 1.2      | 0.130 | 0.042   | 0.119  | 0.117   | 0.128   | 0.128  |

| $200 \times$ | 0.6      | 0.159 | 0.092   | 0.150  | 0.121   | 0.156   | 0.156  |

| $200 \times$ | 1.2      | 0.172 | 0.037   | 0.159  | 0.160   | 0.169   | 0.169  |

| Averag       | ge Error | 0.00% | -35.49% | -4.03% | -16.41% | -4.68%  | -2.46% |

| Maxim        | um Error | 0.00% | -78.56% | -8.76% | -24.03% | -11.93% | -5.83% |

Table 6: Noises on a quiet victim from different algorithms for aligned RLC bus structure

of light in such a dielectric is  $v = \frac{c}{\sqrt{\epsilon\mu}} \approx 2.2 \times 10^8 m/s$ , where c is the speed of light in vacuum. For a 1000  $\mu$ m long wire, the flight time is  $t_f \approx 5$ ps. The flight time is relatively small compared to the signal rising time of 33ps assumed in our experiment, and should not significantly impact the quality of our WCN algorithms. Such speculation has been validated by the following two sets of experiments.

We first study six-bit buses with aggressors shifted as shown in fig.5. In table 7 we present the comparison between different algorithms. Compared to **PES**, the maximum underestimation of **SS**+**AS** is 5.34%, and the average underestimation is less than 3.04%. Such error margins are similar to those for aligned buses in table 6, and **SS**+**AS** is still a close approximation to WCN. On the contrary, **SP** again underestimates WCN by up to 20%.

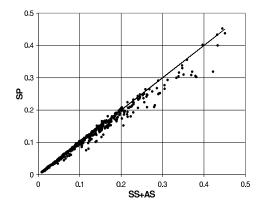

Figure 5: Six-bit unaligned bus

We then study twelve-bit buses. We randomly shield the structure with the total number of shields less than 40% of the total number of wires, and randomly pick a victim and 30-80% normal wires as aggressors. Because **PES** becomes too time consuming to handle such buses, we just compare SS+AS and SP in this set of experiments. In fig.6 we show the experiment results of 500 random cases. Based on this figure, **SP** may severely underestimate the worst case noise. Its maximum underestimation is 35% compared to SS+AS. From the figure we can also see SP may be larger than SS + AS in some cases. The maximum difference for such cases is less than 10% of SS+AS, and the average is even smaller. It has been shown in [1] that **SP** may lead to overestimation of WCN under RC models. Note that **SP** does not provide switching times and patterns that lead to the noise it predicts. Therefore, it is not certain whether such a noise predicted by **SP** may really happen.

Figure 6: Comparison between SS+AS and SP for unaligned bus

# 4.2 Noisy victim

In this section we present experiment results with noisy victims. We carry out experiments with the same six-bit bus structure as shown in section 4.1.1. We provide an artificial noise on the input of the driver to the victim. In table 8, we present the simulation results from different algorithms. We do not compare WCN under RC and RLC models, because in the previous section we have verified that the RC model leads to large underestimation of WCN for GHz+ interconnects. As shown in table 8, compared to **PES**, the maximum underestimation of **SS**+**AS** is 4.62%, and the average underestimation is 2.27%. It is again a very close approximation to **PES**. Superposition severely underestimate WCN, with a maximum underestimation of 39.93% and an average underestimation of 20.53%.

#### 4.3 Experiment summary

We first compare the running time of SS+AS and PESalgorithm. In table 9 we show the average running time for the two algorithms. From the data, We can clearly see that SS+AS uses two to three orders of magnitude less running time than PES does. From all the experiments above, we can conclude that SS+AS achieves much smaller underestimation than SP. Compared to the time consuming PES algorithm, SS+AS uses a fraction of running time but achieves WCN with a maximum underestimation of 5.83% for both aligned and unaligned buses in our experiments. Therefore, SS+AS is the suggested algorithm in practice

| Driver       | Spacing  | PES   | RC WCN  | SS      | SP      | AS      | SS+AS  |

|--------------|----------|-------|---------|---------|---------|---------|--------|

| $30 \times$  | 0.6      | 0.122 | 0.120   | 0.120   | 0.096   | 0.113   | 0.120  |

| $30 \times$  | 1.2      | 0.062 | 0.051   | 0.059   | 0.057   | 0.060   | 0.060  |

| $50 \times$  | 0.6      | 0.141 | 0.122   | 0.140   | 0.116   | 0.126   | 0.140  |

| $50 \times$  | 1.2      | 0.083 | 0.053   | 0.079   | 0.078   | 0.079   | 0.079  |

| $100 \times$ | 0.6      | 0.131 | 0.100   | 0.122   | 0.106   | 0.128   | 0.128  |

| $100 \times$ | 1.2      | 0.113 | 0.042   | 0.106   | 0.096   | 0.113   | 0.113  |

| $150 \times$ | 0.6      | 0.126 | 0.087   | 0.116   | 0.104   | 0.121   | 0.121  |

| $150 \times$ | 1.2      | 0.131 | 0.042   | 0.120   | 0.116   | 0.124   | 0.124  |

| $200 \times$ | 0.6      | 0.138 | 0.081   | 0.122   | 0.112   | 0.132   | 0.132  |

| $200 \times$ | 1.2      | 0.173 | 0.032   | 0.158   | 0.155   | 0.166   | 0.166  |

| Averag       | ge Error | 0.00% | -37.81% | -6.04%  | -14.42% | -4.64%  | -3.04% |

| Maxim        | um Error | 0.00% | -81.60% | -11.87% | -20.47% | -10.71% | -5.34% |

Table 7: Noises on a quiet victim from different algorithms for unaligned RLC bus structure

| 1 | Driver | Spacing  | PES   | $\mathbf{SS}$ | SP      | AS     | SS+AS  | i |

|---|--------|----------|-------|---------------|---------|--------|--------|---|

|   | 30     | 0.6      | 0.405 | 0.396         | 0.243   | 0.402  | 0.402  | f |

|   | 30     | 1.2      | 0.332 | 0.325         | 0.250   | 0.325  | 0.325  | ; |

|   | 50     | 0.6      | 0.539 | 0.524         | 0.366   | 0.507  | 0.524  | 1 |

|   | 50     | 1.2      | 0.486 | 0.480         | 0.407   | 0.466  | 0.480  |   |

|   | 100    | 0.6      | 0.169 | 0.160         | 0.131   | 0.163  | 0.163  | ( |

|   | 100    | 1.2      | 0.124 | 0.114         | 0.111   | 0.124  | 0.124  |   |

|   | 150    | 0.6      | 0.152 | 0.139         | 0.118   | 0.146  | 0.146  |   |

|   | 150    | 1.2      | 0.136 | 0.116         | 0.122   | 0.130  | 0.130  |   |

|   | 200    | 0.6      | 0.162 | 0.154         | 0.125   | 0.160  | 0.160  |   |

|   | 200    | 1.2      | 0.170 | 0.165         | 0.165   | 0.168  | 0.168  |   |

|   | Avera  | ge Error | 0.00% | -5.38%        | -20.53% | -3.15% | -2.27% |   |

|   | Maxim  | ım Error | 0.00% | -14.84%       | -39.93% | -5.85% | -4.62% |   |

Table 8: Noises on a noisy victim from different al-gorithms for aligned RLC bus structure

| Experiment           | PES     | SS+AS      |

|----------------------|---------|------------|

| 6-bit aligned bus    | 10hours | 75seconds  |

| 6-bit unaligned bus  | 18hours | 180seconds |

| 12-bit unaligned bus | 60hours | 635seconds |

| with 3 aggressors    |         |            |

| 6-bit aligned bus    | 30hours | 320seconds |

| with noisy victim    |         |            |

Table 9: Running time of PES and SS+AS.

for deep submicron and GHz+ circuit design.

# 5. CONCLUSION

Previous work has only studied interconnect worst case crosstalk noise (WCN) under RC model. In this work, we have presented the first in-depth study on WCN under RLC model. We have shown that both switching time alignment and switching pattern generation should be considered to obtain WCN under RLC model. We have proposed a new SS+AS algorithm. This algorithm has a linear running time complexity, and uses two to three orders of magnitude less than the running time of the pseudo exhaustive research **PES** in practice. Experiments shows that the **SS+AS** algorithm has an average underestimation of 3% and a maximum underestimation of 5.8% compared to the **PES** algorithm. In contrast, the commonly used superposition algorithm leads to an average underestimation of 15%, and a maximum underestimation of 24%. We have also shown that RC model can result in up to 80% underestimation for

interconnects in predicted ITRS  $0.10\mu m$  technology. Therefore, RLC model is needed to analyze WCN for such GHz+ interconnects.

## 6. **REFERENCES**

- L. H. Chen and M. Marek-Sadowska, "Aggressor alignment for worst-case crosstalk noise," *IEEE Trans.* on Computer-Aided Design of Integrated Circuits and Systems, vol. 20, pp. 612 – 621, May 2001.

- [2] L. He and K. M. Lepak, "Simultaneous shielding insertion and net ordering for capacitive and inductive coupling minimization," in *Proc. Int. Symp. on Physical Design*, 2000.

- [3] N. H. E. Weste and K. Eshraghian, Principles of CMOS VLSI Design: a Systems Perspective. Addison-Wesley, second ed., 1993.

- [4] http://www-device.EECS.Berkeley.EDU/ ptm/.

- [5] J. K. Ousterhout, "Switch-level delay models for digital MOS VLSI," in *Proc. Design Automation Conf*, pp. 542–548, 1984.

- [6] F. Dartu, N. Menezes, J. Qian, and L. T. Pillage, "A gate-delay model for high-speed CMOS circuits," in *Proc. Design Automation Conf*, pp. 576–580, 1994.

- [7] P. D. Gross, R. Arunachalam, K. Rajagopal, and L. T. Pileggi, "Determination of worst-case aggressor alignment for delay calculation," in *Proc. Int. Conf.* on Computer Aided Design, 1998.

- [8] M. Xu and L. He, "An efficient model for frequency-dependent on-chip inductance," in *Great Lakes Symposium on VLSI*, 2001.

- [9] T. Lin and L. Pileggi, "On the efficacy of simplified 2d on-chip inductance models," in *Proc. Design Automation Conf*, 2002.

- [10] L. He, N. Chang, S. Lin, and O. S. Nakagawa, "An efficient inductance modeling for on-chip interconnects," in *Proc. IEEE Custom Integrated Circuits Conference*, pp. 457–460, May 1999.

- [11] M. W. Beattie and L. Pileggi, "IC analyses including extracted inductance model," in *Proc. Design Automation Conf*, 1999.

- [12] Y. Cao, C. M. Hu, X. Huang, A. B. Kahng, S. Muddu, D. Stroobandt, and D. Sylvester, "Effects of global interconnect optimizations on performance estimation of deep submicron design," in *Proc. Int. Conf. on Computer Aided Design*, 2000.