University of California Los Angeles

# Modeling and Optimization of VLSI Interconnects

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Lei He

1999

© Copyright by Lei He 1999 The dissertation of Lei He is approved.

Miodrag Potkonjak

Stephen E. Jacobsen

Milos D. Ercegovac

Jason Cong, Committee Chair

University of California, Los Angeles 1999 To My Wife Shiping Xu.

# TABLE OF CONTENTS

| 1        | Intr | oducti | ion                                                   | 1  |

|----------|------|--------|-------------------------------------------------------|----|

|          | 1.1  | Comp   | uter-Aided Design for VLSI Circuits and Systems       | 1  |

|          | 1.2  | Contr  | ibutions of this Dissertation                         | 5  |

|          | 1.3  | Overv  | iew of the Dissertation                               | 9  |

| <b>2</b> | Win  | esizin | g Optimization for Nets with Multiple Sources         | 15 |

|          | 2.1  | Proble | em Formulation                                        | 17 |

|          |      | 2.1.1  | Multi-Source Wiresizing (MSWS) Problem                | 17 |

|          |      | 2.1.2  | Weighted Delay Formulation                            | 20 |

|          | 2.2  | Prope  | rties of Optimal MSWS Solutions                       | 22 |

|          |      | 2.2.1  | Decomposition of an MSIT                              | 23 |

|          |      | 2.2.2  | Properties of Optimal MSWS Solutions                  | 24 |

|          |      | 2.2.3  | Extensions to Multi-layer Layout                      | 28 |

|          | 2.3  | Prope  | rties of Optimal MSWS/E Solutions                     | 28 |

|          |      | 2.3.1  | Segment-Division and Bundled-Segment                  | 29 |

|          |      | 2.3.2  | Bundled Refinement Property                           | 31 |

|          | 2.4  | Optim  | nal MSWS Algorithm                                    | 33 |

|          |      | 2.4.1  | Bundled Wiresizing Algorithm                          | 33 |

|          |      | 2.4.2  | Optimal Wiresizing Algorithm Using Bundled Refinement | 39 |

|          | 2.5  | Exper  | imental Results                                       | 40 |

|          |      | 2.5.1  | Comparison between Different Wiresizing Solutions     | 42 |

|     |            | 2.5.2  | Speed-up Using Variable Segment-Division                         | 45 |

|-----|------------|--------|------------------------------------------------------------------|----|

|     |            | 2.5.3  | Fidelity of the Elmore Delay Model                               | 45 |

|     | 2.6        | Conclu | usions and Future Work                                           | 49 |

| 3   | AS         | Simple | and Practical 2 1/2-D Capacitance Extraction Method              | -  |

| olo | gy         |        |                                                                  | 52 |

|     | 3.1        | Introd | uction                                                           | 53 |

|     | 3.2        | Found  | ations                                                           | 57 |

|     |            | 3.2.1  | Preliminaries                                                    | 57 |

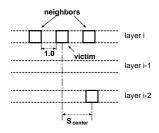

|     |            | 3.2.2  | Coupling between wires on layer $i$ and wires on layer $i-2$     | 59 |

|     |            | 3.2.3  | Coupling between wires on layers $i \pm 2$ and $i \ldots \ldots$ | 63 |

|     |            | 3.2.4  | Coupling between wires on the same layer $\ldots$ .              | 74 |

|     |            | 3.2.5  | Coupling between wires on layer $i$ and wires on layers $i\pm 1$ | 77 |

|     | 3.3        | 2 1/2- | D Methodology                                                    | 78 |

|     |            | 3.3.1  | Capacitance Component Generation                                 | 80 |

|     |            | 3.3.2  | Algorithm for 2 1/2-D Analysis                                   | 83 |

|     |            | 3.3.3  | Examples with 2 $1/2$ -D analysis                                | 84 |

|     | 3.4        | Concl  | usions                                                           | 87 |

|     | <b>T</b> U |        |                                                                  |    |

|     |            | •      | nd Algorithm for Local-Refinement Based Optimiza-                |    |

| t10 | n.         |        |                                                                  | 89 |

|     | 4.1        | Formu  | lations of CH-functions                                          | 91 |

|     | 4.2        | Prope  | rties for CH-programs                                            | 93 |

|     |            | 4.2.1  | Dominance Property                                               | 94 |

|          |      | 4.2.2 General Dominance Property                                    |

|----------|------|---------------------------------------------------------------------|

|          | 4.3  | Local-Refinement based Algorithm                                    |

|          | 4.4  | Comparison with Posynomial Program                                  |

|          | 4.5  | Conclusions and Discussions                                         |

| <b>5</b> | App  | plication of Local-Refinement based Optimization to Simul-          |

| ta       | neou | s Device and Interconnect Sizing                                    |

|          | 5.1  | Formulation and Solution of STIS Problem                            |

|          |      | 5.1.1 Device and Interconnect Models                                |

|          |      | 5.1.2 Problem Formulation                                           |

|          | 5.2  | STIS Algorithm                                                      |

|          |      | 5.2.1 Bound Computation for STIS Problem                            |

|          |      | 5.2.2 Overall Algorithm for STIS Problem                            |

|          | 5.3  | Experimental Results                                                |

|          |      | 5.3.1 Area-Delay Trade-off for Transistor Sizing                    |

|          |      | 5.3.2 Simultaneous Driver and Wire Sizing for Multi-source Nets 126 |

|          |      | 5.3.3 Comparison between Manual Optimization and STIS Al-           |

|          |      | gorithm                                                             |

|          |      | 5.3.4 Comparison between Simple and STL-bounded Models 130          |

|          | 5.4  | Conclusions and Discussions                                         |

| 6        | Арг  | plication of Local-Refinement based Optimization to Simul-          |

| ta       |      | s Interconnect Sizing and Spacing                                   |

|          | 6.1  | Problem Formulation                                                 |

|          |      |                                                                     |

|   |     | 6.1.1  | Introduction                                                                                                 |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------|

|   |     | 6.1.2  | Single-net and Multi-net Interconnect Sizing and Spacing                                                     |

|   |     |        | Problems                                                                                                     |

|   | 6.2 | Prope  | rties and Algorithms                                                                                         |

|   |     | 6.2.1  | Bound Computation for Symmetric SISS Problem 143                                                             |

|   |     | 6.2.2  | Bound Computation for Symmetric GISS Problem 147                                                             |

|   |     | 6.2.3  | Bound Computation for Asymmetric SISS and GISS Prob-                                                         |

|   |     |        | lems                                                                                                         |

|   |     | 6.2.4  | Overall Algorithm for Asymmetric SISS and GISS Problems 151                                                  |

|   | 6.3 | Exper  | imental Results                                                                                              |

|   |     | 6.3.1  | Single-net Interconnect Sizing and Spacing 152                                                               |

|   |     | 6.3.2  | Multi-net Interconnect Sizing and Spacing 156                                                                |

|   | 6.4 | Conclu | usions and Discussions                                                                                       |

| 7 | On- | Chip I | Inductance Model and Its Applications                                                                        |

|   | 7.1 | Introd | uction                                                                                                       |

|   | 7.2 | Found  | ations for Inductance Extraction                                                                             |

|   |     | 7.2.1  | Preliminaries                                                                                                |

|   |     | 7.2.2  | Validation of foundations                                                                                    |

|   | 7.3 | Table- | based Inductance Extraction                                                                                  |

|   | 7.4 | Applie | cations of Inductance Model                                                                                  |

|   |     | 7.4.1  | $L_{eff}$ for coplanar-waveguide $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 172$ |

|   |     | 7.4.2  | Bus optimization                                                                                             |

|   |     |        |                                                                                                              |

|   |        | 7.4.3  | ${\rm Extensions \ to \ Model \ Power/Ground \ Planes \ and \ MCM/PCB}$ |

|---|--------|--------|-------------------------------------------------------------------------|

|   |        |        | Designs                                                                 |

|   | 7.5    | Discus | ssions and Conclusions                                                  |

| 8 | Con    | clusio | ns and Discussions                                                      |

| 9 | App    | endix  | : Proofs for Properties of Optimal MSWS Solutions 185                   |

|   | 9.1    | Prope  | rties of Coefficient Functions                                          |

|   | 9.2    | Proof  | of Theorem 3                                                            |

|   | 9.3    | Proof  | of Theorem 5                                                            |

|   | 9.4    | Proof  | of Theorem 6                                                            |

| R | eferer | nces . |                                                                         |

## LIST OF FIGURES

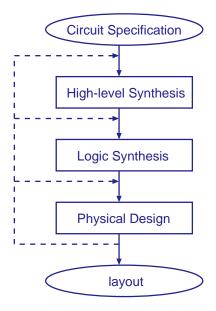

| 1.1 | Overall flow for the computer-aided design of VLSI circuits and                                                                                                                                                                                                                                                                          |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | systems                                                                                                                                                                                                                                                                                                                                  | 3  |

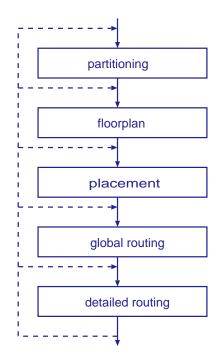

| 1.2 | Conventional flow for physical design.                                                                                                                                                                                                                                                                                                   | 4  |

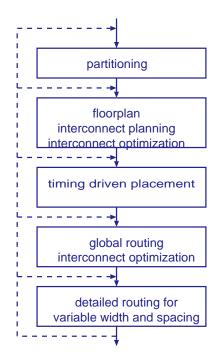

| 1.3 | An innovative physical design flow                                                                                                                                                                                                                                                                                                       | 8  |

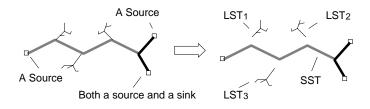

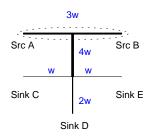

| 2.1 | An $MSIT$ can be decomposed into the source subtree $SST$ , and<br>a set of loading subtrees (three $LST$ s here) branching off from the<br>SST. The dark segments belong to the $SST$                                                                                                                                                   | 23 |

| 2.2 | The optimal wire width assignments for a two-source net with $W$ being the minimum wire width. The $SST$ is surrounded by the dashed curve. Segments outside the curve belong to an $LST$ . The wire width assignment is <i>monotone</i> within the $LST$ . However, the root uni-segment of the $LST$ is wider than uni-segments in the |    |

| 2.3 | SST                                                                                                                                                                                                                                                                                                                                      | 26 |

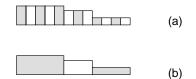

| 3.1 | solution same as that obtained by $\mathcal{E}_F$                                                                                                                                                                                                                                                                                        | 30 |

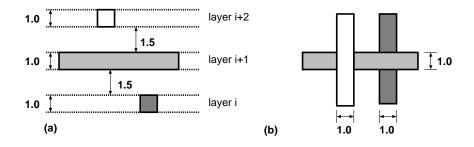

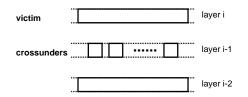

|     | spacings); (b) the top view – all wire have width 1.0. $\ldots$ .                                                                                                                                                                                                                                                                        | 58 |

| 3.2 | Cross-section of a pattern in the first experiment of Section 2.2. $\ .$                        | 60  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 3.3 | Cross-section for a pattern in the second experiment of Section 2.2.                            | 60  |

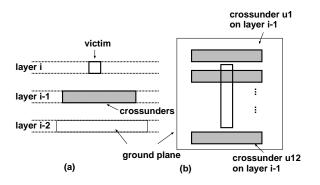

| 3.4 | Cross-section of the real pattern in the first experiment of Section                            |     |

|     | 2.3: the victim on layer $i$ , one crossunder on layer $i - 1$ and a                            |     |

|     | number of wires on layer $i - 2$ . Layer $i - 3$ is a ground plane, but                         |     |

|     | is not shown in the figure                                                                      | 64  |

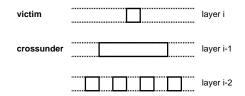

| 3.5 | Layer $i-2$ is modeled as a ground plane: (a) the cross-section                                 |     |

|     | view; (b) the top view. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 65  |

| 3.6 | The geometric structure on layer $i$ for lateral, area and fringe ca-                           |     |

|     | pacitance generation.                                                                           | 81  |

| 3.7 | The geometric structure on layers $i$ and $i+1$ for crossover correction                        |     |

|     | capacitance generation.                                                                         | 83  |

| 3.8 | An example for 2 1/2-D capacitance analysis. $\ldots$ $\ldots$ $\ldots$                         | 83  |

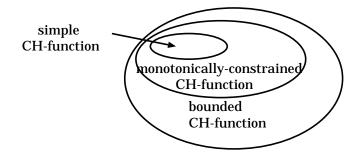

| 4.1 | The simple CH-function is a subset of the monotonically con-                                    |     |

|     | strained CH-function, which is in turn a subset of the bounded                                  |     |

|     | CH-function.                                                                                    | 93  |

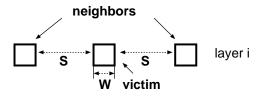

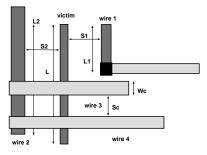

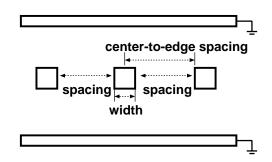

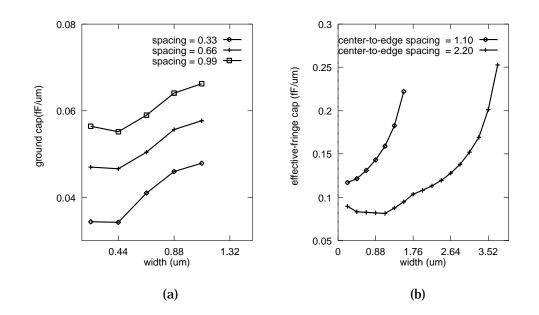

| 6.1 | The basic geometric structure for capacitance extraction                                        | 138 |

| 6.2 | (a) Ground capacitance and (b) effective-fringe capacitance for the                             |     |

|     | central wire (the victim) in the basic geometric structure shown in                             |     |

|     | Figure 6.1. Each curve in (a) has the same spacing but different                                |     |

|     | wire widths, and each curve in (b) has the same center-to-edge                                  |     |

|     | spacing but different wire widths. The capacitance values are given                             |     |

|     | for the unit-length wire.                                                                       | 139 |

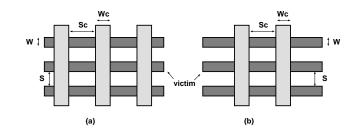

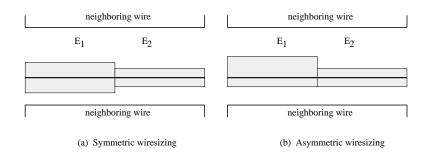

| 6.3 | (a) symmetric wire sizing, and (b) asymmetric wire sizing. The                     |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | asymmetric wire sizing has smaller capacitance and less delay. $\ldots$            | 142 |

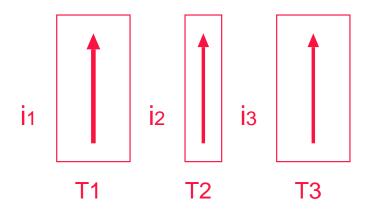

| 7.1 | The cross-section view for a block of $n$ traces, where $T_1$ and $T_n$ are        |     |

|     | dedicated power/ground traces. The widths for the traces are $W_1$ ,               |     |

|     | $W_2$ ,, and $W_n$ , respectively. The spacings between them are $S_1$ ,           |     |

|     | $S_2, \dots$ and $S_{n-1}$ , respectively.                                         | 164 |

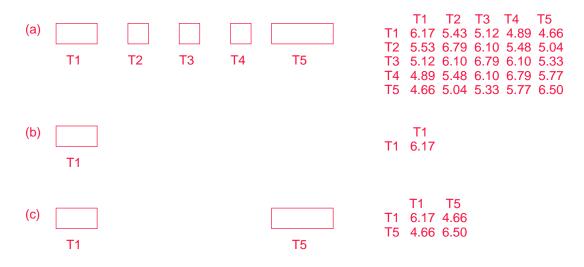

| 7.2 | Loop inductance $(nH)$ by specifying that $T_1$ and $T_5$ are current              |     |

|     | return paths.                                                                      | 165 |

| 7.3 | Partial inductance $(nH)$ without specifying any current return                    |     |

|     | path: (a) a block of size $n = 5$ , (b) only trace $T_1$ (with other               |     |

|     | traces removed), and (c) only two traces $T_1$ and $T_5$ (with traces              |     |

|     | $T_2$ - $T_4$ removed)                                                             | 166 |

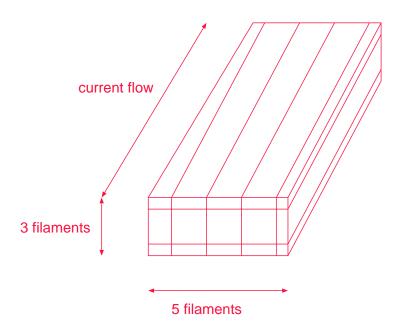

| 7.4 | A trace is divided into $3 \times 5$ filaments. It is assumed that the             |     |

|     | current density is the same within a filament. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 168 |

| 7.5 | The top view of a coplanar-waveguide. $T_1$ and $T_3$ are dedicated                |     |

|     | power/ground traces.                                                               | 172 |

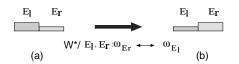

| 9.1 | (a) The width assignments for $E_l$ and $E_r$ in the optimal solution              |     |

|     | $\mathcal{W}^*$ . (b) The wiresizing solution obtained by swapping the width       |     |

|     | assignments for $E_l$ and $E_r$ .                                                  | 187 |

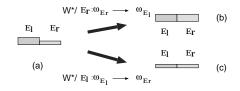

| 9.2 | (a) The width assignments for $E_l$ and $E_r$ in the optimal solution              |     |

|     | $\mathcal{W}^*$ . (b) The wiresizing solution obtained by replacing the width      |     |

|     | of $E_r$ with that of $E_l$ . (c) The wiresizing solution obtained by              |     |

|     | replacing the width of $E_l$ with that of $E_r$                                    | 189 |

|     |                                                                                    |     |

# LIST OF TABLES

| 1.1 | Summary of NTRS'97                                                                                      | 2  |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 2.1 | $gBWSA_L/U$ : Given the minimum uni-segment length $minLength$ ,                                        |    |

|     | an segment-division $\mathcal{E},$ a lower/upper bound $\mathcal{W}_{lower}/\mathcal{W}_{upper}$ of the |    |

|     | optimal wiresizing solution, and a set of possible wire widths $\{W_1,$                                 |    |

|     | $W_2, \ \cdots, \ W_r$ , compute a tight lower/upper bound using BRL or                                 |    |

|     | BRU                                                                                                     | 35 |

| 2.2 | Selective Binary Segment-division Refinement (SBSR): Given the                                          |    |

|     | minimum uni-segment length $minLength$ , an segment-division $\mathcal{E}$ ,                            |    |

|     | a lower bound and an upper bound of the optimal wiresizing solu-                                        |    |

|     | tion, return a refined segment-division                                                                 | 36 |

| 2.3 | $Bundled \ Wire sizing \ Algorithm \ (BWSA): Given \ the \ coarsest \ segment-$                         |    |

|     | division $\mathcal{E}_0$ , the minimum uni-segment length minLength and a                               |    |

|     | set of possible wire widths $\{W_1, W_2, \cdots, W_r\}$ , return the $\mathcal{E}_F$ -tight             |    |

|     | lower and upper bounds of the optimal wiresizing solution. $\ldots$                                     | 37 |

| 2.4 | Parameters based on MCNC $0.5 \mu m$ submicron CMOS technology.                                         | 41 |

| 2.5 | Routing trees for multi-source nets extracted from the layout for                                       |    |

|     | a high-performance Intel microprocessor                                                                 | 42 |

| 2.6 | Multi-source wiresizing results on several nets in an Intel micro-                                      |    |

|     | processor layout. All wires are assumed to be on layer M2                                               | 44 |

| 2.7 | Multi-source wiresizing results on several nets in an Intel micro-                                      |    |

|     | processor layout. We assume that all wires parallel to X-axis are                                       |    |

|     | on layer M1, the rest on layer M2.                                                                      | 44 |

| 2.8 | Running time comparison between GWSA-based and BWSA-based algorithms                                  | 47 |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.9 | Average differences in ranking and SPICE-computed delay for Intel                                     |    |

|     | nets based on $0.5\mu m$ CMOS technology                                                              | 47 |

| 3.1 | $C_{i,i}/C_{i,i-2}$ , where $C_{i,i}$ is total capacitance of the layer- <i>i</i> victim, and         |    |

|     | $C_{i,i-2}$ is its coupling to the wire on layer $i-2$                                                | 61 |

| 3.2 | $C_{i,i}/C_{i,i-2}$ values for the second experiment of Section 2.2                                   | 62 |

| 3.3 | $C_{i,i}/C_{i,i-1}$ , where $C_{i,i}$ is the total capacitance of the victim, and                     |    |

|     | $C_{i,i-1}$ the coupling between the victim and the crossunder                                        | 65 |

| 3.4 | Total capacitance $C_{i,i}$ of the victim on layer $i$ and couplings be-                              |    |

|     | tween the victim and crossunders on layer $i-1$ . $0.50 \mu m$ technology                             |    |

|     | is assumed in the experiment                                                                          | 67 |

| 3.5 | Total capacitance $C_{i,i}$ of the victim on layer $i$ and couplings be-                              |    |

|     | tween the victim and crossunders on layer $i-1$ . $0.35 \mu m$ technology                             |    |

|     | is assumed in the experiment                                                                          | 68 |

| 3.6 | Total capacitance $C_{i,i}$ of the victim on layer $i$ and couplings be-                              |    |

|     | tween the victim and cross<br>unders on layer $i\!-\!1.$ $0.18 \mu m$ technology                      |    |

|     | is assumed in the experiment. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 69 |

| 3.7 | Total capacitance $C_{i,i}$ of the victim on layer $i$ , couplings $C_{i,l1}$                         |    |

|     | and $C_{i,r1}$ between the victim and its same-layer neighbors, and                                   |    |

|     | couplings between the victim and crossunders on layer $i - 1$ or                                      |    |

|     | crossovers on layer $i + 1$ . $0.50 \mu m$ technology is used in this exper-                          |    |

|     | iment.                                                                                                | 71 |

| 3.8  | Total capacitance $C_{i,i}$ of the victim on layer <i>i</i> , couplings $C_{i,l1}$      |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | and $C_{i,r1}$ between the victim and its same-layer neighbors, and                     |     |

|      | couplings between the victim and crossunders on layer $i - 1$ or                        |     |

|      | crossovers on layer $i + 1$ . $0.35 \mu m$ technology is used in this exper-            |     |

|      | iment                                                                                   | 72  |

| 3.9  | Total capacitance $C_{i,i}$ of the victim on layer $i$ , couplings $C_{i,l1}$           |     |

|      | and $C_{i,r1}$ between the victim and its same-layer neighbors, and                     |     |

|      | couplings between the victim and cross<br>unders on layer $i-1$ or                      |     |

|      | crossovers on layer $i + 1$ . $0.18 \mu m$ technology is used in this exper-            |     |

|      | iment                                                                                   | 73  |

| 3.10 | Total capacitance $C_{i,i}$ of the victim wire on layer $i$ and couplings               |     |

|      | $C_{i,l2}, C_{i,l1}, C_{i,r1}$ and $C_{i,r2}$ between the victim wire and its neighbors |     |

|      | $(l_2, l_1, r_1 \text{ and } r_2)$                                                      | 75  |

| 3.11 | Simulated and derived total capacitances of the victim in cases of                      |     |

|      | different neighbor spacing.                                                             | 76  |

| 3.12 | Total capacitances $C_{i,i}$ for the victim in case of different neighbor               |     |

|      | widths                                                                                  | 77  |

| 3.13 | Crossunder couplings between wires $i1, \cdots, i12$ on layer $i$ and the               |     |

|      | cross<br>under on layer $i-1$ with its same-layer neighbors at spacing                  |     |

|      | 1.0 and $\infty$ , for both full and no crossover.                                      | 79  |

| 3.14 | Algorithm for 2 1/2-D analysis                                                          | 85  |

| 3.15 | Comparison between 2 1/2-D analysis and 3-D simulation                                  | 86  |

| 3.16 | Capacitance coefficients for a MCM technology. $c_a, c_f$ and $c_x$ are                 |     |

|      | unit-length area, fringe and lateral capacitances, respectively. $\ . \ .$              | 87  |

| 4.1  | Bound-computation algorithm using the ELR operation                                     | 104 |

| 5.1 | Unit-size effective-resistance for n- and p-transistor                |

|-----|-----------------------------------------------------------------------|

| 5.2 | Delay-area trade-off during transistor sizing on ripple-adders under  |

|     | a $0.5\mu m$ process                                                  |

| 5.3 | Driver and wire sizing for multi-source nets under a $0.5 \mu m$ pro- |

|     | cess. DS+WS – separate driver sizing and wire sizing, STIS –          |

|     | simultaneous driver and wire sizing                                   |

| 5.4 | Comparison between manual optimization and STIS algorithms $~$ . 129  |

| 5.5 | Comparisons between different device and wire sizing formulations 132 |

| 6.1 | Asymmetric GISS algorithm based on ELR and LR operations $152$        |

| 6.2 | Comparison of the average and maximum delays using different          |

|     | algorithms                                                            |

| 6.3 | The convergence rates for the ELR-based bound computation un-         |

|     | der both symmetric and asymmetric SISS formulations. Also shown       |

|     | are the runtimes for SISS algorithms based on dynamic-programming     |

|     | and ELR operations, respectively                                      |

| 6.4 | Convergence of ELR/CE and LR/GE in GISS/ELR algorithm 156 $$          |

| 6.5 | Comparison of different sizing solutions for the bus structure 157    |

- 7.2 Comparison of noise between different buffer insertion solutions. 175

- 7.3 Comparison of noise between different shielding insertion solutions. Column one  $(N_s)$  is the number of signal traces between two shielding trace, and column 2  $(W_s)$  is the width for the shielding traces. Column 3 is the total width (including the total spacing) of the the bus structure, and column 4 is the total wire width. . . . . . 176

- 7.4 Loop inductance computed via numerical extraction for two parallel wire traces in an MCM design. Both wires are 4μm thick, and are 12μm and 21.5μm away from the power plane and ground plane, respectively. The current is assumed to return from power/ground planes. Columns 2-4 are inductance for wire length of 1cm, and columns 5-7 are inductance for wire length of 4cm. For each length, three wire widths are assumed, namely, 19μm, 23μm (i.e., the width has 20% variation compared to width=19μm), and 38μm (i.e., the wire is up-sized by 100% compared to width=19μm). Percentages of inductance changes with respect to inductance values for width=19μm are also given.

#### Acknowledgments

My deep gratitude and appreciation first go to my advisor Prof. Jason Cong for his continuous encouragement, guidance, and support. While giving me the considerable freedom to conduct research on my own, he helped me to develop my skills to identify and solve a research problem, and to present its formulation and solution precisely and clearly. I believe that what I learned from him will guide me well beyond my graduation.

I am also grateful to Prof. Milos D. Ercegovac, Prof. Stephen E. Jacobsen, and Prof. Miodrag Potkonjak, for serving as members of my dissertation committee, and for their many helpful comments. I especially appreciate the help and advice that Prof. Potkonjak has given me on my career planning.

I thank Prof. Andrew B. Kahng for his help in my research. The main results presented in Chapter 3 were from a joint work with him. In addition, Dr. David Noice, Mr. Nagesh Shirali and Dr. Steve H.-C. Yen from Cadence Design Systems, Inc. also provided their inputs and supports.

I enjoyed the opportunity to work with Dr. Norman Chang, Dr. Shen Lin and Dr. O. Sam Nakagawa, during my research internship with Hewlett-Packard Laboratories. Discussions with them stimulated results presented in Chapter 7 (and in a joint paper with them). I especially appreciate Dr. Chang's help and advice for my career planning.

I treasure my experience with UCLA, and would like to thank these wonderful people in the VLSI CAD group and other groups in the Computer Science Department. To name a few, they are Eugene Ding, Patrick H. Madden, Kei-Yong Khoo, John C. Peck Jr., Albert Chung-Wen Tsao, Dennis Jenhsin Huang, Yutao He, Chang Wu, Chin-Chih Chang, Jie Fang, Sung Lim, Songjie Xu. Zhigang Pan helped to collect partial results for comparisons presented in Chapter 6. Ms. Verra Morgan gave me a lot of advice on both academic and personal lives. I owe her a special appreciation.

My deep gratitude and appreciation also go to many people outside UCLA, especially Prof. Lawrence Pileggi, Prof. Sachin Sapatnekar, and Prof. Martin D. F. Wong. They gave me invaluable help and advice on my career planning. Prof. Dian Zhou provided parameters for the MCNC technology used in Chapter 2, and Mr. Heming Chan at Intel Design Technology Department provided multiple source routing examples used in the same chapter.

I am most grateful to my parents, who have always been a source of motivation for me. I dedicate this dissertation to my wife Shiping Xu. This achievement is so humble when compared with her constant support and inspiration, which are more precious during her own journey towards the JD degree from the Stanford Law School.

This work was supported in part by Defense Advanced Research Project Agency (DARPA) under Contracts DAAL01-96-K-3600 and J-FBI-93-112, by the National Science Foundation (NSF) Young Investigator Award MIP9357582, by grants from Intel Corporation and Cadence Design Systems, Inc. under the California MICRO Program, by a GTE Fellowship, and by a Prize for Engineering and Technology from Dimitris N. Chorafas Foundation.

#### Vita

1968 Born, People's Republic of China.

- 1986–1990 B.S. program in Electrical Engineering, Fudan University, Shanghai, China. Top Student Award, 1987 and 1988. Best Graduating Student Award, 1990.

- 1990–1992 Research Associate, VLSI CAD Laboratory, Fudan University. Prototyped a CAD framework environment.

- 1991 Teaching assistant for an upper level undergraduate course: Analog IC Design, Electrical Engineering Dept., Fudan University.

- 1992-1994 MS program in Electrical Engineering, Fudan University. Motorola Fellowship, 1993. Best Paper Award from China's Computer Association CAD/CAM Conference, 1993.

- 1992-1994 Graduate Student Researcher, VLSI CAD Laboratory, Fudan University. Developed a fast-timing simulation tool, and a digital-analog mixed-mode SPICE.

- 1994 Teaching assistant for an upper level undergraduate course: Fundamentals of Statistics, Electrical Engineering Dept., Fudan University.

- 1994 to present PhD Program in Computer Science, UCLA. Prize for Engineering and Technology, the Dimitris N. Chorafas Foundation, 1997.GTE Fellowship, 1998.

| 1994 to present | Graduate Research Assistant, UCLA VLSI CAD Laboratory.              |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------|--|--|--|--|--|

|                 | Working on interconnect-driven design, involving interconnect       |  |  |  |  |  |

|                 | capacitance and inductance extraction, device and interconnect      |  |  |  |  |  |

|                 | modeling, and interconnect-centric layout optimization.             |  |  |  |  |  |

| 1996            | Summer intern, Cadence Design Systems, Inc. Verified and au-        |  |  |  |  |  |

|                 | to<br>mated a 2 $1/2$ -dimensional capacitance extraction methodol- |  |  |  |  |  |

|                 | ogy shipped with the Cadence Silicon Ensemble 5.0 product.          |  |  |  |  |  |

| 1998            | Research intern, Hewlett-Packard Laboratories. Proposed an          |  |  |  |  |  |

|                 | efficient inductance extraction methodology; applied it to in-      |  |  |  |  |  |

efficient inductance extraction methodology; applied it to interconnect analysis, planning, and optimization for the stateof-the-art microprocessor designs.

## Publications

L. He, K. H. Zhang, and P. S. Tang, "An efficient feedback processing method for relaxation based fast timing simulation", in *Proc. IEEE Int'l Symposium on VLSI Technology, Systems, and Applications*, May 1993.

L. He, S. Chen, K. H. Zhang, and P. S. Tang, "Implementation of digital-analog mixed-mode simulation inside SPICE", in *Proc. Int'l Conf. on Computer-Aided Design and Computer Graphics*, Vol. 2, pages 577-81, Aug 1993.

L. He, K. H. Zhang, and P. S. Tang, "A switch-level fast-timing simulator," In

Proc. Int'l Conf. on Computer-Aided Design and Computer Graphics, Vol. 2, pages 565-70, Aug 1993.

Y. Q. Zhang, L. He, J. R. Tong, and P. S. Tang, "An integrated CAD software development environment," *Journal of China's Computer-Aided Design and Computer Graphics*, Vol. 5, No. 3, 1993.

L. He, J. R. Tong, and P. S. Tang, "Development and maintenance of CAD software," *Journal of China's Computer-Aided Design and Computer Graphics*, Vol. 6, No. 1, 1994.

L. He, K. H. Zhang, and P. S. Tang, "Fast timing simulation considering feedback processing," *Journal of China's Electronics*, April 1994.

L. He, K. H. Zhang, and P. S. Tang, "FTSIM: a switch level fast timing simulator," Acta Electronica Sinica, Vol.23, (no.2):17-21, Feb. 1995.

J. Cong and L. He, "Optimal wiresizing for interconnects with multiple sources," in *Proc. ACM/IEEE Int'l Conf. on Computer-Aided Design*, November 1995.

J. Cong and L. He, "Simultaneous transistor and interconnect sizing based on the general dominance property," in *Proc. ACM SIGDA Int'l workshop on Physical Design*, April 1996.

J. Cong and L. He, "Optimal wiresizing for interconnects with multiple sources," ACM Trans. on Design Automation of Electronic Systems, pages 478-511, Oct. J. Cong, L. He, C.-K. Koh, and P. H. Madden, "Performance optimization of VLSI interconnect layout," *Integration, the VLSI Journal (Invited)*, Vol. 21, No. 1&2, pages 1-94, November 1996.

J. Cong and L. He, "An efficient approach to simultaneous transistor and interconnect Sizing," in *Proc. ACM/IEEE Int'l Conf. on Computer-Aided Design*, November, 1996.

J. Cong, L. He, A. B. Kahng, D. Noice, N. Shirali, and S. H.-C. Yen, "Analysis and justification of a simple, practical 2 1/2-D capacitance extraction methodology," in *Proc. ACM/IEEE Design Automation Conference*, pages 627-632, June 1997.

J. Cong, L. He, K.-Y. Khoo, C.-K. Koh, and Z. Pan, "Interconnect design for deep submicron ICs," *Proc. ACM/IEEE Int'l Conf. on Computer-Aided Design* (*Embedded Tutorial*), pages 478–485, November 1997.

J. Cong, L. He, C.-K. Koh, and Z. Pan, "Global interconnect sizing and spacing with consideration of coupling capacitance," *Proc.* ACM/IEEE Int'l Conf. on Computer-Aided Design, pages 628–633, November 1997.

J. Cong and L. He, "An efficient technique for device and interconnect optimization in deep submicron designs," in *Proc. ACM Int'l Symposium on Physical* Design, April 1998. J. Cong and L. He, "Theory and algorithm of local-refinement based optimization with application to device and interconnect sizing," *IEEE Trans. on Computer-Aided Design*, pages 406-420, April 1999.

L. He, N. Chang, S. Lin, and O. S. Nakagawa, "An efficient inductance modeling for on-chip interconnects," in *Proc. IEEE Custom Integrated Circuits Conference*, pages 457-460, May 1999.

### Abstract of the Dissertation

## Modeling and Optimization of VLSI Interconnects

by

### Lei He

Doctor of Philosophy in Computer Science University of California, Los Angeles, 1999 Professor Jason Cong, Chair

As very large scale integrated circuits move into the era of deep-submicron technology and gigahertz clock frequency, the system performance has increasingly become dominated by the interconnect delay. Contributions of this dissertation include the following three related aspects for the design of high-performance interconnects: interconnect modeling, interconnect optimization, and optimization theory.

Concerning interconnect modeling, we study the two extraction problems to compute the capacitance and inductance values respectively from complex 3dimensional interconnect structures. For each problem, we first propose and validate "foundations" that can be used to reduce the problem complexity, then present a simple yet accurate methodology directly based on the foundations. The resulting extraction methodologies are applicable to both IC and MCM/PCB designs, and have been used in the industry for real designs.

Concerning interconnect optimization, we formulate and solve the following three problems:

• The multi-source wire sizing (MSWS) problem. It determines the optimal

widths for all wire segments to minimize the delay along a given routing tree with multiple sources.

- The simultaneous transistor and interconnect sizing (*STIS*) problem using the accurate device model. It assigns optimal wire widths to interconnects and optimal sizes to transistors to minimize the delay for multiple critical paths, where a path may contain multiple routing trees and related devices.

- The global interconnect sizing and spacing (GISS) problem. Given the topology for multiple routing trees, the GISS problem finds the wire sizing and spacing solution *simultaneously* for all trees, with consideration of coupling capacitance between them.

We reveal interesting properties and present efficient algorithms for all those problems. Experiments show that our formulations and algorithms have achieved significant reduction of the interconnect delay.

As to the optimization theory, we formulate three classes of optimization problems: the simple, monotonically constrained, and bounded CH-problems. We reveal that the dominance property holds for those CH-problems under different types of local-refinement operations. This property immediately leads to an efficient polynomial-time algorithm, which provides a unified solution to a number of interconnect optimization problems, including the MSWS, STIS, and GISS problems.

# CHAPTER 1

# Introduction

# 1.1 Computer-Aided Design for VLSI Circuits and Systems

Following the prediction of the Moore's Law [57], the complexity of integrated circuits was doubled for every 18 months in the past three decades. As projected by the 1997 National Technology Roadmap for Semiconductors(NTRS'97) [78] (see Table 1.1), this exponential growth will continue for at least another decade, and a single-chip with 21 million transistors and more than 1 gigahertz clock frequency is expected by the end of this year (1999). Given such a high complexity and clock frequency, the only feasible way to finish the design within a reasonable amount of time is the computed-aided design.

As shown in Figure 1.1, the computer-aided design of VLSI circuits and systems is typically divided into the following stages:

- *High level synthesis*: based on the circuit specifications, to generate the system behavior by RTL-level components, and to define the function for each component.

- Logic synthesis: to generate functions of RTL-level components by boolean expressions, and to implement boolean expressions by logic gates given in the library.

| Tech. $(\mu m)$             | 0.25 | 0.18 | 0.15            | 0.13 | 0.10             | 0.07 |

|-----------------------------|------|------|-----------------|------|------------------|------|

| Year                        | 1997 | 1999 | 2001            | 2003 | 2006             | 2009 |

| Transistor $\#$             | 11M  | 21M  | $40 \mathrm{M}$ | 76M  | $200 \mathrm{M}$ | 520M |

| Across chip clock (MHz)     | 750  | 1200 | 1400            | 1600 | 2000             | 2500 |

| Area $(mm^2)$               | 300  | 340  | 385             | 430  | 520              | 620  |

| Wiring levels               | 6    | 6-7  | 7               | 7    | 7-8              | 8-9  |

| Min. wire width $(\mu m)$   | 0.25 | 0.18 | 0.15            | 0.13 | 0.10             | 0.07 |

| Min. wire spacing $(\mu m)$ | 0.34 | 0.24 | 0.21            | 0.17 | 0.14             | 0.10 |

| Wire aspect ratio           | 1.8  | 1.8  | 2.0             | 2.1  | 2.4              | 2.7  |

Table 1.1: Summary of NTRS'97

• *Physical design*: to implement logic gates by geometric patterns, and to place and connect these geometric patterns to obtain the layout for fabrication.

Different objectives such as area, delay and power minimizations are often shared among these stages. Iterations between stages or within a stage are sometimes needed. For example, a failed physical design procedure may lead to a logic re-synthesis, or another physical design procedure based on the current logic synthesis result. Simulations are invoked after each stage to verify the function and timing correctness, and may lead to more iterations.

The last stage, physical design, contains the topics studied in this dissertation. It is also called *layout* design. For a layout, the geometric implementation for a logic gate is a *cell*. A set of related cells is a *block*, which often implement a specific logic function. Connection points on the block or cell are *pins*. A *net* is a set of pins to be electrically connected. Then, an integrated circuit (*IC*) can be represented by a *netlist*, which is a set of nets. Five iterative steps are involved

Figure 1.1: Overall flow for the computer-aided design of VLSI circuits and systems.

in the physical design process, namely, partitioning, floorplanning, placement, global routing and detailed routing (see Figure 1.2).

Partitioning is the first step for the physical design procedure. For the purpose of "divide-and-conquer", partitioning divides the netlist into a set of sub-netlist. Each sub-netlist contains a number of blocks, and is small enough to be handled by the design tools, or the silicon implementation capacities such as the maximum die area for ICs. The objective for partitioning often is to minimize the total number of nets that belong to more than one sub-netlist.

Floorplanning and placement determine shapes, orientations and locations for blocks and cells on a layout. Floorplanning handles *flexible* blocks whose shapes and orientations are not yet fully determined. Placement deals with *fixed* blocks that have specific layout and orientations. The objective for floorplanning and placement is to avoid overlap of blocks and cells, and to minimize the total wire

Figure 1.2: Conventional flow for physical design.

length and the chip area.

Global and detailed routing complete the electrical connections (via metal wires) between blocks or cells as indicated by the netlist. The entire routing area is divided into disjoint, smaller routing regions. Global routing only assigns each net to a set of routing regions to minimize the total routing area and the congestion in routing regions. The detailed routing implements nets within each and every routing region by metal wires with exact geometric specifications including layer assignments. In this dissertation, metal wires are also called as *interconnects* or *wires*.

### **1.2** Contributions of this Dissertation

As very large scale integrated circuits move into the era of deep-submicron technology and gigahertz clock frequency, the system performance has increasingly become dominated by the interconnect delay [33, 22]. Therefore, interconnect modeling and optimization is drawing considerable attention. Contributions of this dissertation include the following three related aspects for the design of high-performance interconnects: interconnect modeling, interconnect optimization, and optimization theory.

We study the following interconnect modeling problems:

- Interconnect capacitance extraction problem. It computes the capacitance values from complex 3-dimensional interconnect structures. We propose and validate five "foundations" that can be used to simplify capacitance extraction, then present a simple yet accurate 2 1/2-dimensional extraction methodology directly based on the foundations. This methodology is able to generate capacitance on fly during interconnect design and optimization, and can be used for both IC and MCM/PCB designs.

- Interconnect inductance extraction problem. It computes the inductance values from three-dimensional on-chip interconnect structures. Our approach is based on the partial inductance model. It is accurate and efficient, and again can be used during the interconnect design and optimization procedure. It has been used to generate distributed RLC models for on-chip interconnects with consideration of process variations, and has been extended to MCM/PCB designs. In addition, several design freedoms, including buffer insertion and shielding insertion, are studied to reduce the inductive effect.

We also investigate the following interconnect optimization problems:

- Multi-source wire sizing (MSWS) problem. For this problem, we are given a routing tree with multiple sources. The goal is to determine the optimal widths for all wire segments such that the delay is minimized. We further study the wire sizing problem without an *a priori* fixed wire segmenting, which allows us to use much finer wire segmenting for more delay reduction or less wire area, but still to be able to find the optimal solution in a timely manner.

- Simultaneous transistor and interconnect sizing (STIS) problem. We assume that the circuit netlist is given and the routing topology is fixed, and apply device models more accurate compared to many used in interconnect optimization works. We then assign optimal wire widths to all wire segments and optimal sizes to all transistors for minimizing the delay and/or power for multiple critical paths. Here, a path contains several nets/routing-trees. Compared to the single-net sizing problems such as the MSWS problem, this problem has a much higher complexity but is able to achieve more delay and power reduction.

- Global interconnect sizing and spacing (GISS) problem. Given the topology for multiple nets, the GISS problem finds the wire sizing and spacing solution optimal to all nets, with consideration of coupling capacitance between neighboring wires. The formulation uses coupling capacitance generated on fly during wire sizing and spacing procedure, and can be treated as part of the STIS problem. Therefore, we are able to consider simultaneous device sizing, and wire sizing and spacing for multiple paths, using accurate models for device delay and interconnect coupling capacitance.

In addition, this dissertation makes a nice contribution to the theory of the local-refinement (LR) based optimization. We formulate three classes of optimization problems: the simple, monotonically constrained, and bounded CH-programs. We reveal the dominance property (Theorem 8) under the local refinement (LR) operation for the simple CH-program, as well as the general dominance property (Theorem 9) under the pseudo-LR operation for the monotonically constrained CH-program and under the extended-LR operation for the bounded CH-program. These properties enable a very efficient polynomial-time algorithm, using different types of LR operations to compute tight lower and upper bounds of the exact solution to any CH-program. The formulation and algorithm for CH-programs unify solutions to several important CAD problems, including the MSWS, STIS, and GISS problems. Other algorithmic contributions will be summarized in Section 1.3, with details in Chapters 2-7.

Formulations and solutions to these problems belong to the general framework of the *interconnect design and optimization* problem. Given the netlist to connect devices, the problem is to determine the interconnect topologies, wire sizing and spacing solutions, buffer locations and sizes, driver/receiver sizes, and shielding insertion. The objective can be optimizing delay, power, signal integrity, and skew (in case of clock nets).

The solution to the interconnect design and optimization problem can be used in an innovative physical design flow to better handle the interconnect delay. As shown in Figure 1.3, the innovative physical design flow is different from the conventional physical design in the following aspects:

During floorplanning, *interconnect planning* is carried out simultaneously with planning for logic blocks. Based on certain estimation models (see [32] for an example on interconnect delay estimation considering the impact of wire sizing),

Figure 1.3: An innovative physical design flow.

the impact of wire sizing and spacing, interconnect coupling noise, shielding insertion, and buffer insertion must be considered by the interconnect planning. On the other hand, detailed but quick interconnect optimization may be carried out for critical nets. At the same time, placement should explicitly consider timing constraints, rather than simply minimize the total wire length. In addition, interconnect optimization techniques, especially buffer insertion, should be considered to meet time constraints.

Global routing extensively applies interconnect optimization to synthesize interconnect structures, including topologies, wire ordering and shielding solutions, wire widths and spacings, layer assignments, and buffer locations and sizes. Then, detailed routing geometrically implements the synthesized interconnect structures with multiple widths and spacings. For the sake of completeness, a post-layout interconnect optimization can be invoked to further refine wire widths and spacings, and device sizes, with consideration of the exact configuration of interconnect structures.

## 1.3 Overview of the Dissertation

The remainder of the dissertation includes the following parts:

In Chapter 2, we study the multiple-source wiresizing (MSWS) problem. Our contributions include:

- We formulate the wiresizing problem to minimize delay for nets with multiple sources under the distributed RC model. Decomposing an MSIT into a source subtree (SST) and a set of loading subtrees (LSTs), we show a number of interesting properties of the optimal wiresizing solutions under this decomposition, including the LST separability, the LST monotone property, the SST local monotone property, and the dominance property. These properties lead to effective algorithms to compute the optimal wire width assignment for any given MSIT. We have tested our algorithm on multisource nets extracted from the multi-layer layout of a high-performance Intel processor. HSPICE simulation shows that our methods reduce the average delay by up to 23.5% and the maximum delay by up to 37.8% for the submicron CMOS technology.

- We study the optimal wiresizing problem using a variable segment-division rather than an *a priori* fixed segment-division used in all previous works. We show the bundled refinement property that leads to a very efficient wire sizing algorithm based on bundled refinement operations and the segmentdivision refinement operations. The algorithm yields a speedup of over 100x

time and does not lose any accuracy, when compared to the method based on an *a priori* fixed segment-division. The algorithm has been extensively used in the practice.

• We also investigate the *fidelity* of the Elmore delay model for wiresizing optimization using a ranking technique. We have found that the optimal wiresizing solution selected according to the Elmore delay model is about 0.06% worse than the optimal wiresizing solution selected according to the SPICE-computed delay, when the delays of both solutions are measured by SPICE simulation. This experiment convincingly justifies our formulation based on the Elmore delay model for the current submicron CMOS technology.

These results were first presented in [14, 16]. To the best of our knowledge, it is the first work which presents an in-depth study of both the optimal wiresizing problem for MSITs and the optimal wiresizing problem under a *variable* segmentdivision.

In Chapter 3, we address interconnect capacitance extraction during interconnect optimization. Our contributions include:

- We show how basic drivers in process technology (planarization and minimum metal density requirements) actually simplify the extraction problem; we do this by proposing and validating five "foundations" through detailed experiments with a 3-D field solver on representative 0.50μm, 0.35μm and 0.18μm process parameters.

- We present a simple yet accurate 2 1/2-D extraction methodology directly based on the foundations. This methodology has been productized and is being shipped with the Cadence Silicon Ensemble 5.0 product for the timing

verification purpose. The methodology is also able to generate capacitance on fly during interconnect design and optimization, and can be used for both IC and MCM/PCB designs.

These results were first presented in [21].

In Chapter 4, we present the theory and algorithm for local-refinement based optimization. Our contributions in this chapter include:

- We formulate three classes of optimization problems: the simple, monotonically constrained, and bounded CH-programs. The simple CH-program contains the single-source and multi-source wire sizing problems, and is a subset of the monotonically constrained CH-program. In turn, the monotonically constrained CH-program is a subset of the bounded CH-program.

- We generalize the concept of the LR operation, and introduce the concepts of the pseudo-LR operation and the extended-LR operation. We then reveal the dominance property (Theorem 8) under the LR operation for the simple CH-program, as well as the general dominance property (Theorem 9) under the pseudo-LR operation for the monotonically constrained CH-program and under the extended-LR operation for the bounded CH-program.

- Based on the dominance property and the general dominance property we propose a very efficient polynomial-time algorithm, using different types of LR operations to compute tight lower and upper bounds of the exact solution to any CH-program.

These results were first presented in [20, 19, 25]. Note that both the MSWS problem in Chapter 2 and the STIS and GISS problems to be presented in Chapters 5 and 6 belong to CH-programs. Therefore, the formulation and algorithm of CH-programs unify the solutions to all three problems. In Chapter 5, we study the simultaneous transistor and interconnect sizing (STIS) problem. Our contributions include:

- We assume that the circuit netlist is given and routing topology is fixed, and then formulate the STIS problem to assign optimal wire widths to all wire segments and optimal sizes to all transistors, for minimizing the delay and/or power for multiple critical paths. Compared to the single-net sizing problems such as the MSWS problem, this problem has much higher complexity but is able to achieve more delay and power reduction.

- We apply the LR-based bound-computation algorithm presented in Chapter 4 to the STIS problem under both the simple device model and the accurate STL-bounded device model. The STL-bounded model is based on tables pre-computed from SPICE simulations for the device delay, so that it is much more accurate than many models used in previous device and interconnect optimization algorithms. Experiments show that the boundcomputation algorithm can efficiently handle both simple and STL-bounded models, and obtain solutions close to the global optimum in both cases. According to SPICE simulations, the solution obtained by the STIS algorithm under the simple model achieves up to 14.4% delay reduction when compared to the solution given by manual optimization (reported in [10]). Furthermore, the solution obtained by the STIS algorithm under the accurate STL-model achieves up to 15.1% additional delay reduction when compared to the solution obtained by the STIS algorithm under the simple model.

These results were first presented in [20, 19, 25], and were among the first in-depth studies on the simultaneous interconnect and device sizing problems.

In Chapter 6, we study the interconnect sizing and spacing problem for the single-net and multiple nets, respectively. Our contributions include:

- We formulate the global interconnect sizing and spacing (GISS) problem based on the concept of asymmetric wire sizing. Given the topology for multiple nets, the problem finds the wire sizing and spacing solution optimal for all nets, and considers coupling capacitance extracted during wire sizing and spacing procedure.

- We pose the GISS problem as a CH-program, which directly leads to an effective and efficient solution based on bound computation using different types of local-refinement operations. Note that this GISS formulation can be treated as part of the STIS formulation. Therefore, we have a unified formulation and solution to the problem of simultaneous device sizing, and wire sizing and spacing for multiple paths, under accurate models for device delay and interconnect coupling capacitance.

- We also solve the single-net interconnect sizing and spacing (SISS) problem. It is a simpler version of the GISS problem assuming that neighboring wires are fixed for the specific net. Experiments show that GISS algorithm may achieve up to 39% delay reduction, when compared with SISS algorithm applied iteratively to multiple nets.

These results were first presented in [23, 19, 25], and were among the first indepth studies of the global interconnect sizing and spacing problem using accurate capacitance model.

In Chapter 7, we study the inductance extraction problem for on-chip interconnects. Our contributions include:

- We propose and *theoretically* validate two foundations which allow us to reduce the problem size of inductance extraction without loss of accuracy, and present a table-based inductance extraction methodology directly based on the two foundations.

- We use this efficient inductance extraction methodology to generate distributed RLC models for on-chip interconnects with consideration of process variations. We have applied this RLC model to interconnect modeling and optimization for designs of the state-of-the-art microprocessors in Hewlett-Packard Company.

These result were first present in [44]. To the best of our knowledge, it is the first work that presents an efficient and accurate table-based inductance extraction method for on-chip interconnects. Note that the table-based inductance extraction has been recently extended to off-chip interconnects in MCM/PCB designs.

In Chapter 8, we discuss the future works and conclude the dissertation. Finally, several proofs for the MSWS problem are presented in the Appendix (Chapter 9).

# CHAPTER 2

# Wiresizing Optimization for Nets with Multiple Sources

All wiresizing works [30, 29, 73, 82, 7, 6, 56, 83] and simultaneous device and wire sizing works [26, 55, 49] assume that there is a unique source in each interconnect tree (called *single source interconnect tree* (SSIT)) and minimize the delay between the source and a set of critical sinks. However, there exist many important interconnect structures with multiple potential sources, each driving the interconnect at a different time, such as those in global signal buses. We call such interconnect structures as *multi-source interconnect trees* (MSITs). Even those single-source wiresizing algorithms based on the mathematical programming [72, 56, 55, 82, 6] or the sensitivity analysis [73, 83] might be adapted to minimize the delay between the multiple source-sink pairs by modifying their objective functions, none of existing sizing works explicitly considers MSITs. It is of both theoretical and practical interest to understand the properties of the optimal wiresizing solutions for MSITs and develop efficient algorithms directly for MSITs.

In this chapter, we study the multiple-source wiresizing (MSWS) problem. Our contributions include:

• We formulate the wiresizing problem to minimize delay for nets with multiple sources under the distributed RC model. Decomposing an MSIT into a source subtree (SST) and a set of loading subtrees  $(LST_s)$ , we show a number of interesting properties of the optimal wiresizing solutions, including the LST separability, the LST monotone property, the SST local monotone property, and the dominance property. These properties lead to effective algorithms to compute the optimal wire width assignment for any given MSIT. We have tested our algorithm on multi-source nets extracted from the multi-layer layout of a high-performance Intel processor. SPICE simulation shows that our methods reduce the average delay by up to 23.5% and the maximum delay by up to 37.8% for the submicron CMOS technology.

- We also study the optimal wiresizing problem using a variable segmentdivision rather than an *a priori* fixed segment-division used in all previous works. We show the bundled refinement property that leads to a very efficient wire sizing algorithm based on bundled refinement operations and the segment-division refinement operations. The algorithm yields a speedup of over 100x time and does not lose any accuracy, when compared to the method based on an *a priori* fixed segment-division.

- Finally, we investigate the fidelity of the Elmore delay model for wiresizing optimization using the ranking technique similar to [4]. We have found that the optimal wiresizing solution selected according to the Elmore delay model is about 0.06% worse than the optimal wiresizing solution selected according to the SPICE-computed delay, when the delays of both solutions are measured by SPICE simulation. This experiment convincingly justifies our formulation based on the Elmore delay model for the current submicron CMOS technology.

Those results are first presented in [14, 16]. To the best of our knowledge, it is the first work which presents an in-depth study of both the optimal wiresizing problem for MSITs and the optimal wiresizing problem under a *variable* segmentdivision.

The remainder of this chapter is organized as follows: In Section 2.1, we present the formulation of the *MSIT* wiresizing problem. In Section 2.2 and 2.3, we study the properties of the optimal wiresizing solutions for *MSIT* designs, under the *a priori* fixed and the variable segment-divisions, respectively. These properties lead to efficient algorithms given in Section 2.4. Section 2.5 shows experimental results, including the fidelity study of the Elmore delay model. Section 2.6 concludes the chapter with discussions of future works. The proofs of the Theorems 3, 5 and 6 are given in the Appendix at the ending of this proposal. Proofs of other theorems, together with more experimental results, can be found in a technical report [15].

# 2.1 Problem Formulation

# 2.1.1 Multi-Source Wiresizing (MSWS) Problem

We call the wiresizing problem for MSITs as the multi-source wiresizing (MSWS) problem. For an MSIT, each pin in the MSIT can be a source (driver), or a sink (receiver), or both at different times. We assume, however, no two sources in the MSIT are active at the same time. Let a node be either a pin or a Steiner point in the MSIT and src(MSIT) the set of pins which can be sources of the MSIT, we say that  $sink^i(MSIT)$  is the set of sinks in the MSIT when pin  $N_i$  is the source of the MSIT. Besides, let a segment connect two nodes and  $\{S_1, S_2, \dots, S_m\}$  be the set of segments in the MSIT. In order to capture the distributed resistive property of interconnects and achieve better wiresizing solutions, a segment is divided into a sequence of uni-segments. The term of "uni-segment" is coined based on this assumption that the wire width is uniform within a uni-segment. The segment-division determines the set of all uni-segments,  $\{E_1, E_2, \dots, E_n\}$ , in the MSIT. Our wiresizing problem is formulated to find a wire width for each unisegment from a set of given choices  $\{W_1, W_2, \dots, W_r\}$   $(W_1 < W_2 < \dots < W_r)$ . Different from our formulation, a segment in [29] is not further divided and is simply treated as a uni-segment<sup>1</sup>, and a segment in [26] is divided into a sequence of wires of unit length and such a wire of unit length is treated as a uni-segment. Thus, both segment-divisions in [29, 26] are given a priori and fixed during the wiresizing procedure. In our formulation, the segment-division is in fact a variable during the wiresizing procedure and is defined by the wiresizing procedure, which will be discussed later in Section 2.3. For simplicity, we assume that an a priori fixed segment-division is given in this section.

The modeling technique similar to those used in [29] is applied. Each unisegment is treated as a  $\pi$ -type RC circuit containing resistance  $r_E$  and capacitance  $c_E$ , respectively. Let the unit-width unit-length wire have wire resistance  $r_0$ , wire area capacitance  $c_a$  and wire fringing capacitance  $c_f$ , then  $r_E = r_0 \cdot \frac{l_E}{w_E}$  and  $c_E = c_a \cdot w_E \cdot l_E + c_f \cdot l_E$  for uni-segment E with width  $w_E$  and length  $l_E$ . The driver at source  $N_i$  is modeled by an output capacitance  $C_d^i$  and a fixed-value resistor  $R_d^i$  connected to an idle voltage source, and the receiver at sink  $N_j$  by a loading capacitor  $c_s^j$ . Thus, a given interconnect including its drivers and receivers is modeled by a distributed RC tree. The Elmore delay [37]  $t^{ij}$  in the RC tree from source  $N_i$  to sink  $N_j$  is a function of the segment-division  $\mathcal{E}$  and the wiresizing solution  $\mathcal{W}$ . It can be written as the Eqn. (2.1) according to the Elmore delay

<sup>&</sup>lt;sup>1</sup>we note that artificial degree-2 Steiner points can be introduced within a segment in [29] to achieve certain segment-division.

formulation for RC trees [65].

$$t^{ij}(MSIT, \mathcal{E}, \mathcal{W}) = \sum_{E \in P(N_i, N_j)} r_E \cdot \left(\frac{c_E}{2} + C_E\right)$$

(2.1)

where the summation is taken over all uni-segments on the unique path  $P(N_i, N_j)$ from source  $N_i$  to sink  $N_j$ , and  $C_E$  is the total downstream capacitance of unisegment E with respect to source  $N_i$ . In order to handle multiple source-sink pairs, we further introduce the following weighted delay formulation Eqn. (2.2).

$$t(MSIT, \mathcal{E}, \mathcal{W}) = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot t^{ij}(MSIT, \mathcal{E}, \mathcal{W})$$

(2.2)

where  $\lambda^{ij}$  is the penalty weight to indicate the priority of the Elmore delay  $t^{ij}$  between source  $N_i$  and sink  $N_j$ .

With these definitions, we give the general formulation of the MSWS problem as follows:

Formulation 1 Given an MSIT, a segment-division  $\mathcal{E}$  and a set of possible wire width choices, the multi-source wiresizing (MSWS) problem for delay minimization is to determine a wiresizing solution  $\mathcal{W}$  which gives a wire width  $w_E$  for every uni-segment E under  $\mathcal{E}$ , such that the weighted delay  $t(MSIT, \mathcal{E}, \mathcal{W})$  is minimized.

When there is only one source in an interconnect tree, the MSWS problem degenerates into the *single-source wiresizing* (SSWS) problem. Note that we assume a given segment-division in Formulation 1. A more general wiresizing problem, the multi-source wiresizing problem *without* an *a priori* given segment-division (*the* MSWS/E problem) will be presented in Section 2.3.

# 2.1.2 Weighted Delay Formulation

For simplicity, we assume that all interconnects belong to the same layer and the assumption will be removed later in Section 2.2.3. It is not difficult to verify that the Elmore delay  $t^{ij}$  between source  $N^i$  and sink  $N^j$  can be formulated as follows:

$$t^{ij}(MSIT, \mathcal{E}, \mathcal{W})$$

$$= \mathcal{K}_{0}^{ij} + \mathcal{K}_{1}^{i} \cdot \sum_{E \in MSIT} l_{E} \cdot w_{E} +$$

$$\mathcal{K}_{2} \cdot \sum_{E,E' \in MSIT} f^{ij}(E, E') \cdot \frac{l_{E} \cdot l_{E'} \cdot w_{E'}}{w_{E}} +$$

$$\mathcal{K}_{3} \cdot \sum_{E,E' \in MSIT} f^{ij}(E, E') \cdot \frac{l_{E} \cdot l_{E'}}{w_{E}} +$$

$$\mathcal{K}_{4} \cdot \sum_{E} g^{ij}(E) \cdot \frac{l_{E}}{w_{E}} + \mathcal{K}_{5} \cdot \sum_{E \in MSIT} h^{ij}(E) \cdot \frac{l_{E}^{2}}{w_{E}} \qquad (2.3)$$

where  $w_E$  and  $l_E$  are respectively the (wire) width and length of the uni-segment E.  $\mathcal{K}_0^{ij}, \mathcal{K}_1^i, \mathcal{K}_2, \cdots, \mathcal{K}_5$  are constants independent of the wiresizing solution, as given in the following:

$$\begin{split} \mathcal{K}_{0}^{ij} &= R_{d}^{i} \cdot C_{d}^{i} + R_{d}^{i} \cdot \sum_{u \in sink^{i}(MSIT)} c_{s}^{u} + R_{d}^{i} \cdot \sum_{E \in MSIT} c_{f} + \sum_{E \in P(N_{i},N_{j})} \frac{r_{0} \cdot c_{a}}{2} \\ \mathcal{K}_{1}^{i} &= R_{d}^{i} \cdot c_{a} \\ \mathcal{K}_{2} &= r_{0} \cdot c_{a} \\ \mathcal{K}_{3} &= r_{0} \cdot c_{f} \\ \mathcal{K}_{4} &= r_{0} \\ \mathcal{K}_{5} &= \frac{r_{0} \cdot c_{f}}{2} \end{split}$$

Recall that  $R_d^i$  and  $C_d^i$  are the driving resistance and output capacitance for the driver at source  $N_i$ , and  $c_s^u$  the sink capacitance at sink  $N_u$ . These parameters can take account the different sizes of drivers/receivers at different sources/sinks of an MSIT. Besides,  $f^{ij}(E, E'), g^{ij}(E)$  and  $H^{ij}(E)$  defined below, again, are constants independent of the wiresizing solution.

$$f^{ij}(E,E') = \begin{cases} 1 & if \ E \in P(N_i,N_j) \ and \ E' \in Des^i(E) \\ 0 & otherwise \end{cases}$$

(2.4)

$$g^{ij}(E) = \begin{cases} \sum_{u \in sink^{i}(E)} c_{s}^{u} & if \ E \in P(N_{i}, N_{j}) \\ 0 & otherwise \end{cases}$$

(2.5)

$$h^{ij}(E) = \begin{cases} 1 & if \ E \in P(N_i, N_j) \\ 0 & otherwise \end{cases}$$

(2.6)

where  $Des^{i}(E)$  is the set of downstream uni-segments of E with respect to source  $N_{i}$ , and  $sink^{i}(E)$  the set of downstream sinks of E with respect to source  $N_{i}$ .

Assume that  $\lambda^{ij}$ 's are normalized, i.e.,

$$\sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} = 1$$

the objective function Eqn. (2.2) becomes:

$$t(MSIT, \mathcal{E}, \mathcal{W})$$

$$= \mathcal{K}_{0} + \mathcal{K}_{1} \cdot \sum_{E \in MSIT} l_{E} \cdot w_{E} +$$

$$\mathcal{K}_{2} \cdot \sum_{E, E' \in MSIT} F(E, E') \cdot \frac{l_{E} \cdot l_{E'} \cdot w_{E'}}{w_{E}} +$$

$$\mathcal{K}_{3} \cdot \sum_{E, E' \in MSIT} F(E, E') \cdot \frac{l_{E} \cdot l_{E'}}{w_{E}} +$$

$$\mathcal{K}_{4} \cdot \sum_{E \in MSIT} G(E) \cdot \frac{l_{E}}{w_{E}} + \mathcal{K}_{5} \cdot \sum_{E \in MSIT} H(E) \cdot \frac{l_{E}^{2}}{w_{E}} \qquad (2.7)$$

where

$$\mathcal{K}_0 = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot K_0^{ij}$$

(2.8)

$$\mathcal{K}_1 = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot K_1^i$$

(2.9)

$$F(E, E') = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot f^{ij}(E, E')$$

(2.10)

$$G(E) = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot g^{ij}(E)$$

(2.11)

$$H(E) = \sum_{N_i \in src(MSIT)} \sum_{N_j \in sink^i(MSIT)} \lambda^{ij} \cdot h^{ij}(E)$$

(2.12)

Our MSWS problem is aimed to find the optimal  $w_E$ 's to minimize the weighted delay formulation Eqn. (2.7). Although this weighted delay formulation for multiple sources and multiple sinks is very similar to that for the single source and multiple sinks in [29], the coefficient functions F, G and H have very different properties, which lead to much higher complexity and very different properties for the MSWS problem when compared to the SSWS problem. These properties will be discussed in Section 2.2.

# 2.2 Properties of Optimal MSWS Solutions

The single-source wiresizing problem (SSWS) under the an a priori fixed segmentdivision was studied in [29], and the polynomial-time optimal algorithm was developed based on the separability, the monotone property and the dominance property. The presence of multiple sources, however, greatly complicates the wiresizing problem. For example, with multiple sources, even a monotone wiresizing solution is not well defined. Nevertheless, our research have revealed a number of interesting properties of the optimal MSWS solutions under the decomposition of MSITs. Some of them generalize the results on the SSWS problem, and others are unique for the MSWS problem. These properties to be presented in this section and Section 2.3 will enable us to apply the algorithms developed in [29] to the MSWS problem to certain extent and to develop even more efficient algorithms in Section 2.4.

#### 2.2.1 Decomposition of an MSIT

When there is only one source in the routing tree, each segment has a unique signal direction and the ancestor-descendant can be defined with respect to the direction. The MSWS problem is most complicated by the fact that, in general, there is no fixed signal direction for a segment. In order to reduce the complexity with the MSWS problem, we decompose an MSIT into the source subtree (SST) and a set of loading subtrees (LSTs) (see Figure 2.1). The SST <sup>2</sup> is the subtree spanned by all source nodes in the MSIT. After we remove the SST from the MSIT, the remaining segments form a set of subtrees, each of them is called an LST. When every pin of an MSIT can be a source at different times, the entire MSIT becomes the SST and there is no LST.

Figure 2.1: An MSIT can be decomposed into the source subtree SST, and a set of loading subtrees (three LSTs here) branching off from the SST. The dark segments belong to the SST.