INTEGRATION, the VLSI Journal 21 (1996) 1-94

# INTEGRATION Report (Invited) Performance optimization of VLSI interconnect layout

Jason Cong\*, Lei He, Cheng-Kok Koh, Patrick H. Madden

Department of Computer Science, School of Engineering and Applied Science, University of California, 4711 Boelter Hall, Los Angeles, CA 90095, USA

Received 8 July 1996; revised 15 August 1996

#### Abstract

This paper presents a comprehensive survey of existing techniques for interconnect optimization during the VLSI physical design process, with emphasis on recent studies on interconnect design and optimization for high-performance VLSI circuit design under the deep submicron fabrication technologies. First, we present a number of interconnect delay models and driver/gate delay models of various degrees of accuracy and efficiency which are most useful to guide the circuit design and interconnect optimization process. Then, we classify the existing work on optimization of VLSI interconnect into the following three categories and discuss the results in each category in detail: (i) topology optimization for high-performance interconnects, including the algorithms for total wire length minimization, critical path length minimization, and delay minimization; (ii) device and interconnect sizing, including techniques for efficient driver, gate, and transistor sizing, optimal wire sizing, and simultaneous topology construction, buffer insertion, buffer and wire sizing; (iii) high-performance clock routing, including abstract clock net topology generation and embedding, planar clock routing, buffer and wire sizing for clock nets, non-tree clock routing, and clock schedule optimization. For each method, we discuss its effectiveness, its advantages and limitations, as well as its computational efficiency. We group the related techniques according to either their optimization techniques or optimization objectives so that the reader can easily compare the quality and efficiency of different solutions.

#### Contents

| 1. lr | ntroduction                                   | 2  | 3.2. Topology optimization for path length        |    |

|-------|-----------------------------------------------|----|---------------------------------------------------|----|

| 2. P  | reliminaries                                  | 3  | minimization                                      | 21 |

| 2.    | .1. Interconnect delay models                 | 5  | 3.2.1. Tree cost/path length tradeoffs            | 21 |

| 2.    | .2. Driver delay models                       | 11 | 3.2.2. Arboresences                               | 23 |

| 3. T  | opology optimization for high-performance     |    | 3.2.3. Multiple source routing                    | 26 |

| in    | nterconnect                                   | 16 | 3.3. Topology optimization for delay minimization | 28 |

| 3.    | 1. Topology optimization for total wirelength |    | 4. Wire and device sizing                         | 31 |

|       | minimization                                  | 17 | 4.1. Device sizing                                | 31 |

|       | 3.1.1. Minimum spanning trees                 | 17 | 4.1.1. Driver sizing                              | 32 |

|       | 3.1.2. Conventional Steiner tree algorithms   | 17 | 4.1.2. Transistor and gate sizing                 | 33 |

<sup>\*</sup> Corresponding author. Tel.: 1310 206 2775; Fax: 1310 825 2273; e-mail: cong@cs.ucla.edu.

| 4.1.3. Buffer insertion  4.2. Wire sizing optimization  4.2.1. Wire sizing to minimize weighted delay 4.2.2. Wire sizing to minimize maximum delay or achieve target delay  4.3. Simultaneous device and wire sizing 4.3.1. Simultaneous driver and wire sizing 4.3.2. Simultaneous gate and wire sizing 4.3.3. Simultaneous transistor and wire sizing 4.3.4. Simultaneous buffer insertion and wire sizing 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction  4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 5.1. Abstract topology generation  5.2. Embedding of abstract topology generation  5.2. Embedding of abstract topology 5.2.1. Zero-skew embedding 5.2.2. Bounded-skew embedding 5.2.3. Topology generation with embedding 5.3.1. Max—Min planar clock routing 5.3.2. Planar-DME clock routing 5.4.3. Buffer and wire sizing for clock nets 5.4.1. Wire sizing in clock routing 5.4.2. Buffer insertion in clock routing 5.4.3. Buffer insertion and sizing in clock routing 5.4.4. Buffer insertion and wire sizing in clock routing 5.5. Non-tree clock routing 5.6. Clock schedule optimization 5.7. Clock schedule optimization 5.7. Somultaneous transition 5.7. Somultaneous transition and wire sizing in clock routing 5.8. High-performance clock routing 5.9. Abstract topology generation 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and wire sizing in clock routing 5.9. Somultaneous transition and sizing in clock routing 5.9. Somultaneous transition and sizing in clock routing 5.9. Somultaneous transition and sizing in clock routing 5.9. Somultaneous transition a |                           |                                             |    |                                             |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------|----|---------------------------------------------|----|

| 4.2.1. Wire sizing to minimize weighted delay 4.2.2. Wire sizing to minimize maximum delay or achieve target delay 4.3. Simultaneous device and wire sizing 4.3.1. Simultaneous driver and wire sizing 4.3.2. Simultaneous gate and wire sizing 4.3.3. Simultaneous transistor and wire sizing 4.3.4. Simultaneous buffer insertion and wire sizing 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 5.1. Abstract topology generation  5.2. Bounded-skew embedding 5.2.2. Bounded-skew embedding 5.2.3. Topology generation with embedding 5.2.3. Planar clock routing 5.3.1. Max—Min planar clock routing 5.3.2. Planar-DME clock routing 5.3.3. Buffer and wire sizing for clock nets 5.4.1. Wire sizing in clock routing 5.4.2. Buffer insertion in clock routing 5.4.3. Buffer insertion and wire sizing in clock routing 5.4.4. Buffer insertion and wire sizing in clock routing 5.5.5. Non-tree clock routing 5.6. Clock schedule optimization 5.7.5. Abstract topology generation 5.6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.1                       | .3. Buffer insertion                        | 37 | 5.1.2. Bottom-up topology generation        | 57 |

| 4.2.2. Wire sizing to minimize maximum delay or achieve target delay  4.3. Simultaneous device and wire sizing  4.3.1. Simultaneous driver and wire sizing  4.3.2. Simultaneous gate and wire sizing  4.3.3. Simultaneous transistor and wire sizing  4.3.4. Simultaneous buffer insertion and wire sizing  4.4. Simultaneous topology construction and sizing  4.4. Simultaneous transistor and sizing  4.4. Simultaneous topology construction and sizing  4.4. Simultaneous transitor and wire sizing during topology construction  4.4. Simultaneous tree construction, buffer insertion and wire sizing  5. High-performance clock routing  5. High-performance clock routing  5. High-performance clock routing  5. Clock schedule optimization  5. Clock schedule optimization  5. Simultaneous wire sizing during topology generation  5. Clock schedule optimization  5. Clock schedule optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2. Wi                   | re sizing optimization                      | 38 | 5.2. Embedding of abstract topology         | 59 |

| or achieve target delay  4.3. Simultaneous device and wire sizing  4.3.1. Simultaneous driver and wire sizing  4.3.2. Simultaneous gate and wire sizing  4.3.3. Simultaneous gate and wire sizing  4.3.4. Simultaneous buffer insertion and wire sizing  4.4. Simultaneous topology construction and sizing  4.4.1. Dynamic wire sizing during topology construction  4.4.2. Simultaneous tree construction, buffer insertion and wire sizing  5. High-performance clock routing  5. Abstract topology generation  4.4. Simultaneous driver and wire sizing  4.5. Simultaneous transistor and wire sizing  4.7 Simultaneous transistor and wire sizing  4.8 Simultaneous transistor and wire sizing  4.9 Simultaneous transistor and wire sizing  5. A.1. Wire sizing in clock routing  5. A.2. Buffer insertion and sizing in clock routing  5. Simultaneous tree construction, buffer clock routing  5. Simultaneous tree construction, buffer insertion and wire sizing in clock routing  5. Simultaneous tree construction, buffer clock routing  5. Simultaneous tree construction, buffer insertion and wire sizing in clock routing  5. Simultaneous tree construction, buffer clock routing  5. Simultaneous tree construction and sizing of clock routing  5. Simultaneous tree construction and sizing of clock routing  5. Simultaneous tree construction and sizing of clock routing  5. Simultaneous tree clock routing  5. Simultaneous tree construction and sizing  5. Simultaneous tree clock routing  5. Simultaneous tree clock routing  5. Simultaneous tree clock routin | 4.2                       | .1. Wire sizing to minimize weighted delay  | 39 | 5.2.1. Zero-skew embedding                  | 59 |

| 4.3. Simultaneous device and wire sizing 4.3.1. Simultaneous driver and wire sizing 4.3.2. Simultaneous gate and wire sizing 4.3.3. Simultaneous transistor and wire sizing 4.3.4. Simultaneous buffer insertion and wire sizing 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 5. High-performance clock routing 5. Ala Buffer insertion and wire sizing in clock routing 5. Ala Buffer insertion and wire sizing in clock routing 5. Simultaneous tree construction, buffer insertion and wire sizing 5. Clock schedule optimization 5. Conclusion and future work 5. Conclusion and future work 5. Simultaneous device and wire sizing 5. Simultaneous transistor and wire sizing 5. Simultaneous tree and wire sizing 5. Simultaneous tree construction, buffer clock routing 5. Simultaneous tree construction, buffer insertion and wire sizing in clock routing 5. Conclusion and future work 5. Conclusion and future work 5. Simultaneous tree and wire sizing 5. Simultaneous tree and wire sizing 5. Simultaneous tree and wire sizing 5. Simultaneous tree construction, buffer clock routing 5. Simultaneous tree construction and sizing in clock routing 5. Simultaneous tree construction and sizing in clock routing 5. Simultaneous tree construction and sizing in clock routing 5. Simultaneous tree construction and sizing in clock routing 5. Simultaneous tree construction and sizing in clock routing 5. Simultaneous tree construction  | 4.2                       | .2. Wire sizing to minimize maximum delay   |    | 5.2.2. Bounded-skew embedding               | 62 |

| 4.3.1. Simultaneous driver and wire sizing 4.3.2. Simultaneous gate and wire sizing 4.3.3. Simultaneous transistor and wire sizing 4.3.4. Simultaneous buffer insertion and wire sizing 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 5. High-performance clock routing 5. Ala Buffer insertion and wire sizing in 5. Clock schedule optimization 5. Conclusion and future work 5. Conclusion and future work 5. Ala Buffer insertion clock routing 5. Conclusion and future work 6. Simultaneous tree construction 6. Simultaneous tree clock routing 6. Simultaneous tree clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction, buffer 6. Simultaneous tree clock routing 6. Simultaneous tree clock routing 6. Simultaneous tree clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tree construction and sizing in clock routing 6. Simultaneous tr |                           | or achieve target delay                     | 44 | 5.2.3. Topology generation with embedding   | 66 |

| 4.3.2. Simultaneous gate and wire sizing 4.3.3. Simultaneous transistor and wire sizing 4.3.4. Simultaneous buffer insertion and wire sizing 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 5. High-performance clock routing 5. All Buffer insertion in clock routing 5. High-performance clock routing 5. Clock schedule optimization 5. Conclusion and future work 5. All Buffer insertion and wire sizing in clock routing 5. Clock schedule optimization 5. Conclusion and future work 5. Clock schedule optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3. Sin                  | nultaneous device and wire sizing           | 47 | 5.3. Planar clock routing                   | 68 |

| 4.3.3. Simultaneous transistor and wire sizing 49 5.4. Buffer and wire sizing for clock nets 70 4.3.4. Simultaneous buffer insertion and wire sizing 51 5.4.2. Buffer insertion in clock routing 74 5.4.3. Simultaneous topology construction and sizing 51 5.4.3. Buffer insertion in clock routing 78 4.4.1. Dynamic wire sizing during topology construction 52 5.4.4. Buffer insertion and wire sizing in clock routing 79 5.5.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 81 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.3                       | .1. Simultaneous driver and wire sizing     | 47 | 5.3.1. Max-Min planar clock routing         | 68 |

| 4.3.4. Simultaneous buffer insertion and wire sizing 51 5.4.2. Buffer insertion in clock routing 74 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 52 5.4.4. Buffer insertion and wire sizing in clock routing 78 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 79 5. High-performance clock routing 54 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3                       | .2. Simultaneous gate and wire sizing       | 48 | 5.3.2. Planar-DME clock routing             | 69 |

| wire sizing 51 5.4.2. Buffer insertion in clock routing 74 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 52 5.4.4. Buffer insertion and wire sizing in clock routing 79 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 81 5. High-performance clock routing 54 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.3                       | .3. Simultaneous transistor and wire sizing | 49 | 5.4. Buffer and wire sizing for clock nets  | 70 |

| 4.4. Simultaneous topology construction and sizing 4.4.1. Dynamic wire sizing during topology construction 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.4.4. Buffer insertion and wire sizing in clock routing 79 clock routing 79 5.5. Non-tree clock routing 51 5.4.3. Buffer insertion and sizing in clock 78 79 79 79 79 79 79 79 79 79 79 79 79 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.3                       | .4. Simultaneous buffer insertion and       |    | 5.4.1. Wire sizing in clock routing         | 71 |

| 4.4.1. Dynamic wire sizing during topology construction 52 5.4.4. Buffer insertion and wire sizing in 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 51 5.6. Clock schedule optimization 52 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | wire sizing                                 | 51 | 5.4.2. Buffer insertion in clock routing    | 74 |

| construction 52 5.4.4. Buffer insertion and wire sizing in 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 81 5. High-performance clock routing 54 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.4. Sin                  | nultaneous topology construction and sizing | 51 | 5.4.3. Buffer insertion and sizing in clock |    |

| 4.4.2. Simultaneous tree construction, buffer insertion and wire sizing 52 5.5. Non-tree clock routing 81 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4                       | .1. Dynamic wire sizing during topology     |    | routing                                     | 78 |

| insertion and wire sizing 52 5.5. Non-tree clock routing 81 5. High-performance clock routing 54 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           | construction                                | 52 | 5.4.4. Buffer insertion and wire sizing in  |    |

| 5. High-performance clock routing 54 5.6. Clock schedule optimization 82 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.4                       | .2. Simultaneous tree construction, buffer  |    | clock routing                               | 79 |

| 5.1. Abstract topology generation 55 6. Conclusion and future work 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           | insertion and wire sizing                   | 52 | 5.5. Non-tree clock routing                 | 81 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol><li>High-pe</li></ol> | rformance clock routing                     | 54 | 5.6. Clock schedule optimization            | 82 |

| 5.1.1. Top-down topology generation 56 References 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |                                             | 55 | 6. Conclusion and future work               | 83 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1.                      | .1. Top-down topology generation            | 56 | References                                  | 86 |

#### 1. Introduction

The driving force behind the rapid growth of the VLSI technology has been the constant reduction of the feature size of VLSI devices (i.e. the minimum transistor size). The feature size decreased from about 2 µm in 1985, to about 1 µm in 1990, and to 0.35-0.5 µm today (1996). The prediction is that it will be reduced to about 0.18 µm in year 2001 [1]. Such continual miniaturization of VLSI devices has strong impact on the VLSI technology in several ways. First, the device density on integrated circuits grows quadratically with the rate of decrease in the feature size. As a result, the total number of transistors on a single VLSI chip has increased from less than 500 000 in 1985 to over 10 million today. The prediction is that it will reach 64 million in year 2001 [1]. Second, the devices operate at a higher speed, and the interconnect delay becomes much more significant. According to the simple scaling rule described in [2], when the devices and interconnects are scaled down in all three dimensions by a factor of S, the intrinsic gate delay is reduced by a factor of S, the delay of local interconnects (such as connections between adjacent gates) remains the same, but the delay of global interconnects increases by a factor of  $S^2$ . As a result, the interconnect delay has become the dominating factor in determining system performance. In many systems designed today, as much as 50-70% of clock cycle are consumed by interconnect delays. This percentage will continue to rise as the feature size decreases further.

Not only do interconnects become more important, they also become much more difficult to model and optimize in the deep submicron VLSI technology, as the *distributed nature* of the interconnects has to be considered. Roughly speaking, the interconnect delay is determined by the driver/gate resistance, the interconnect and loading capacitance, and the interconnect resistance. For the conventional technology with the feature size of 1 µm or above, the interconnect resistance in most cases is negligible compared to the driver resistance. So, the interconnect and loading gates can be modeled as a lumped loading capacitor. In this case, the interconnect delay is determined by the driver resistance times the total loading capacitance. Therefore, conventional optimization

techniques focus on reducing the driver resistance using driver, gate, and transistor sizing, and minimizing the interconnect capacitance by buffer insertion and minimum-length, minimum-width routing. For the deep submicron technology which became available recently, the interconnect resistance is comparable to the driver resistance in many cases. As a result, the interconnect has to be modeled as a distributed RC or RLC circuit. Techniques such as optimal wire sizing, optimal buffer placement, and simultaneous driver, buffer, and wire sizing have become necessary and important.

This paper presents an up-to-date survey of the existing techniques for interconnect optimization during the VLSI layout design process. Section 2 discusses interconnect delay models and gate delay models and introduces a set of concepts and notation to be used for the subsequent sections. Section 3 presents the techniques for *interconnect topology optimization*, where the objective is to compute the best routing pattern for a net for interconnect delay minimization. It covers the algorithms based on total wirelength minimization, pathlength minimization, and delay minimization. Section 4 presents the techniques for *device and interconnect sizing*, which determines the best geometric dimensions of devices and interconnects for delay minimization. It includes driver sizing, transistor sizing, buffer placement, wire sizing, and combinations of these techniques. Section 5 discusses techniques for *high-performance clock routing*, including clock tree topology generation and embedding, planar clock routing, buffer and wire sizing for clock nets, non-tree clock routing, and clock schedule optimization. Section 6 concludes the paper with suggestions of several directions for future research.

#### 2. Preliminaries

VLSI design involves a number of steps, including high-level design, logic design, and physical layout. Designs are generally composed of a number of functional blocks or cells which must be interconnected. This paper addresses the interconnection problems of these blocks or cells.

A net N is composed of a set of pins  $\{s_0, s_1, s_2, \ldots, s_n\}$  which must be made electrically connected.  $s_0$  denotes the driver of the net, which supplies a signal to the interconnect. In some cases, a net may have multiple drivers, each driving the interconnect at a different time (such as in a signal bus). These nets are called *multi-source* nets. The remaining pins in a net are sinks, which receive the signal from the driver.

The *interconnection* of a net consists of a set of wire segments (often in multiple routing layers) connecting all the pins in the net. It can be represented by a graph, in which each edge denotes a wire segment and each vertex denotes a pin or joint of two wire segments. Interconnections are generally rectilinear.

In this paper, we will primarily be interested in interconnect trees, in which there exists a unique simple path between any pair of nodes. We use Path(u, v) to denote the unique path from u to v in the interconnect tree.  $d_T(u, v)$  denotes the path length of Path(u, v). The source node  $s_0$  will generally be referred to as the root of an interconnect tree, each node v in a tree is connected to its parent by edge  $e_v$ . We use  $T_v$  to denote the subtree of T that is rooted at v. Given an edge e, we use Des(e) to denote the set of edges in the subtree rooted at e (excluding e), Ans(e) to denote the set of edges  $\{e' \mid e \in Des(e')\}$  (again, excluding e), and  $T_e$  to denote the subtree of T rooted at e, i.e.,  $Des(e) \cup \{e\}$ . The topology of an interconnect tree T refers to an abstraction of T on the Manhattan

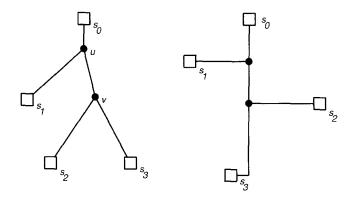

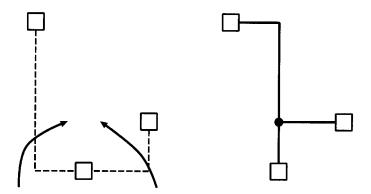

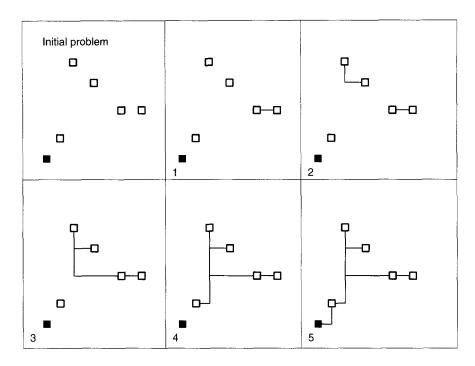

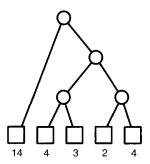

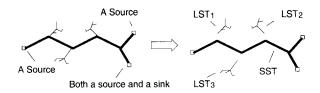

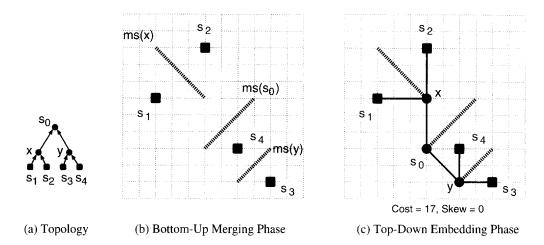

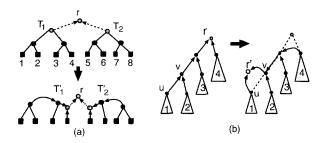

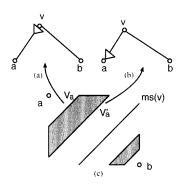

Fig. 1. The abstract topology of an interconnect tree, and its embedding.

plane, without considering the wire width, routing layer assignment, and all electrical properties. In this paper, we often use an interconnect tree and its topology interchangeably.

However, we distinguish an interconnect tree T from its abstract topology G, which is a binary tree (with the possible exception at the root) such that all sinks are the leaf nodes of the binary tree. The source driver is the root node of the tree, and may have a singleton internal node as its only child. Consider any two nodes, say u and v, with a common parent node w = p(u) = p(w) in the abstract topology; then the signal from the source has to pass through w before reaching u and v (and their descendants). The topology of an interconnect tree T is an embedding of the abstract topology G, i.e. each internal node  $v \in G$  is mapped to a location  $l(v) = (x_v, y_v)$  in the Manhattan plane, where  $(x_v, y_v)$  are the x- and y-coordinates, and each edge  $e \in G$  is replaced by a rectilinear edge or path. Fig. 1 shows an abstract topology and its embedding (which is not unique). Some interconnect optimization algorithms first compute a good abstract topology and then generate an optimal or near-optimal embedding.

The definitions and notation for interconnect tree T also apply to abstract topology G. For example, we also use Path(u,v) to denote the unique path from u to v in the abstract topology G. Furthermore, we define the *level* of a node in an abstract topology. The root node of the abstract topology is at level 0, and the children of a node at level k are at level k+1. A node with a smaller level number is at a higher level of the hierarchy.

In this paper, we are mainly concerned with the Manhattan (rectilinear) distance metrics. We use d(u,v) to denote the Manhattan distance between points u and v. If edge e connects u and v, then  $|e| \ge d(u,v)$ . Note that we differentiate between d(u,v) and  $d_T(u,v)$ ; in general,  $d_T(u,v) \ge d(u,v)$ . The distance between two pointsets P and Q is defined as  $d(P,Q) = \min\{d(p,q) \mid p \in P, q \in Q\}$ , while the diameter of a point set P is diameter  $(P) = \max\{d(p,q) \mid p,q \in P\}$ , and the radius of a point set P with respect to some point c is radius  $(P) = \max\{d(p,c) \mid p \in P\}$ .

An interconnect tree T is evaluated on a number of attributes, including cost and delay. Generally, the cost of edge e refers to its wire length, and is denoted by |e|. For instances where we consider variably sized wires, with the width of edge e denoted by  $w_e$ , the cost of edge e may refer to its area (i.e., the product of its length and width,  $|e|w_e$ ). |T| denotes the total cost of all edges in tree T.

Let t(u, v) denote the signal delay from node u to node v. Then,  $t(s_0, s_i)$  denotes the delay from source to sink  $s_i$ . For simplicity, we use  $t_i$  to denote  $t(s_0, s_i)$ . A brief discussion on the various delay

models can be found in Sections 2.1 and 2.2. We are also interested in the *skew* of the clock signal, defined to be the difference in the clock signal delays to the sinks. One common definition of the *skew* of clock tree T is given by  $skew(T) = \max_{s_i, s_j \in S} |t_i - t_j|$ .

Let r,  $c_a$  and  $c_f$  denote the unit square wire resistance, unit area capacitance, and unit length fringing capacitance (for 2 sides), respectively. Then, the wire resistance of edge e, denoted  $r_e$ , and the total wire capacitance of e, denoted  $c_e$ , are given as follows:

$$r_e = \frac{r|e|}{w_e}, \qquad c_e = c_a|e|w_e + c_f|e|.$$

We use  $\operatorname{Cap}(v)$  to denote the total capacitance of  $T_v$ . We will use  $R_d$  as the resistance of the driver, and  $c_{s_i}^s$  to denote the sink capacitance of  $s_i$ . We will use  $\operatorname{Cap}(\mathscr{S})$  as the capacitance of all the sink nodes. We will use  $\operatorname{sink}(T_v)$  to denote the set of sinks in  $T_v$ .

## 2.1. Interconnect delay models

As VLSI design reaches deep submicron technology, the delay model used to estimate interconnect delay in interconnect design has evolved from the simplistic lumped RC model to the sophisticated high-order moment matching delay model. In the following, we will briefly describe a few commonly used delay models in the literature of interconnect performance optimization. Although our discussion will center around RC interconnect, some of the models are not restricted to RC interconnect. For a more comprehensive list of references on RLC interconnect, the interested reader may refer to [3].

In the *lumped RC model*, "R" refers to the resistance of the driver and "C" refers to the total capacitance of the interconnect and the total gate capacitance of the sinks. The model assumes that wire resistance is negligible. This is generally true for circuits with feature sizes of  $1.2 \,\mu m$  and above since the driver resistance is substantially larger than the total wire resistance. In this case, the switching time of the gate dominates the time for the signal to travel along the interconnect and the sinks are considered to receive the signal at the same time due to the negligible wire resistance.

However, as the feature size decreases to the submicron dimension, the wire resistance is no longer negligible. Sinks that are farther from the source generally have a longer delay. For example, under the *path length* (or *linear*) delay model, the delay from u to v in an interconnect tree is proportional to the sum of edgelengths in the unique u-v path, i.e.,  $t(u,v) \propto \sum_{e_u \in Path(u,v)} |e_w|$ . The limitation of the path length delay model is that it ignores the wire resistance but consider only wire capacitance along the path. Moreover, it ignores the effect of edges not along the path. The merit of the path length delay model is that routing problems for path length control or optimization are generally much easier than delay optimization under more sophisticated delay models to be presented below.

The delay models presented in the remainder of this section consider both wire resistance and capacitance of the interconnect. Under these models, the interconnect is modeled as an RC tree, which is recursively defined as follows [4]: (i) a lumped capacitor between ground and another node is an RC tree, (ii) a lumped resistor between two non-ground nodes is an RC tree, (iii) an RC line with no dc path to ground is an RC tree, and (iv) any two RC trees (with common ground) connected together to a non-ground node is an RC tree. We can extend the above definition for RLC tree easily by considering inductors and RLC lines.

Given an RC tree, Rubinstein et al. [4] compute a uniform upper bound of signal delay at every node, denoted  $t_P$ , as follows:

$$t_P = \sum_{\text{all nodes } k} R_{kk} C_k, \tag{1}$$

where  $C_k$  is the capacitance of the lumped capacitor at node k and  $R_{ki}$  is defined to be the resistance of the portion of the (unique) path  $Path(s_0, i)$  that is common to the (unique) path  $Path(s_0, k)$ . In particular,  $R_{kk}$  is the resistance between the source and node k. There are a few advantages of this model: (i) it is simple, yet captures the distributed nature of the circuit; (ii) it gives a uniform delay upper bound and is easier to use for interconnect design optimization; and (iii) it correlates reasonably well with the Elmore delay model, which will be discussed next.

The *Elmore delay model* [5] is the most commonly used delay model in recent works on interconnect design. Under the Elmore delay model, the signal delay from source  $s_0$  to node i in an RC tree is given by [4]

$$t(s_0, i) = \sum_{\text{all nodes } k} R_{ki} C_k. \tag{2}$$

Unlike the upper bound signal delay model in Eq. (1), each sink (and in fact, all nodes in the RC tree) has a separate delay measure under the Elmore delay model. It is used to estimate the 50% delay of a monotonic step response (to a step input) by the mean of the impulse response, which is given by  $\int_0^\infty th(t) dt$  where h(t) is the impulse response. The impulse response h(t) can be viewed as either (i) the response to the unit impulse (applied at time 0) at time t, or (ii) the derivative of the unit step response at time t. The 50% delay, denoted  $t_{50}$ , is the time for the monotonic step response to reach 50% of  $V_{\rm DD}$ , and it is the median of the impulse response. It can be shown that the Elmore delay gives the 63% (= 1 - 1/e) delay of a simple RC circuit (with a single resistor and a single capacitor), which is an upper bound of the 50% delay. In general, the Elmore delay of a sink in an RC tree is a (loose) absolute upper bound on the actual 50% delay of the sink under the step input [6].

The main advantage of the Elmore delay is that it provides a simple closed-form expression with greatly improved accuracy for delay measure compared to the lumped RC model. In the following, we illustrate that the Elmore delay can be expressed as a simple algebraic function of the geometric parameters of the interconnect, i.e., the lengths and widths of edges, and parasitic constants such as the sheet resistance, unit wire area capacitance and unit fringing capacitance of the interconnect.

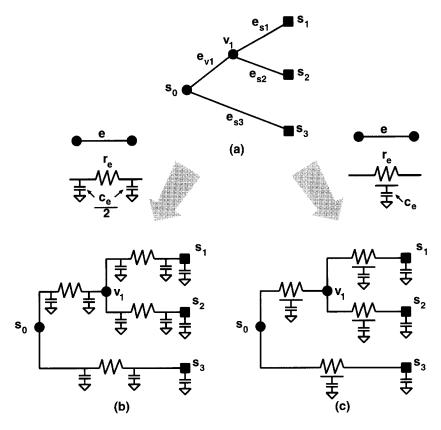

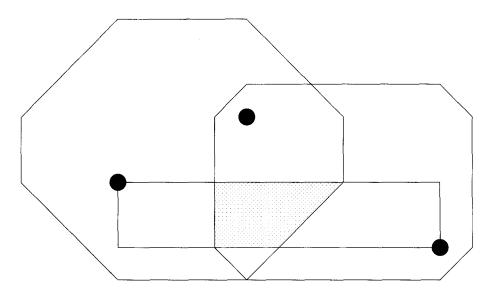

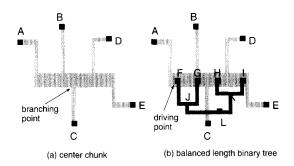

Consider an interconnect T in Fig. 2. To model an interconnect as an RC tree, an edge e in the interconnect in (a) can be modeled as a  $\pi$ -type circuit with a lumped resistor of resistance  $r_e$  and two capacitors, each of capacitance  $c_e/2$ , where  $r_e$  and  $c_e$  are the wire resistance and capacitance of edge e as shown in (b). Other lumped circuit models such as L- and T-type circuits may be used to model an edge as well [2]. It is also possible to model an edge as a distributed RC line as shown in (c).

In the case of each wire segment modeled as a  $\pi$ -type circuit as in Fig. 2(b), we can write the Elmore delay from the source to sink  $s_i$  in terms of the geometry of the interconnect, i.e., |e| and

In general, the x% delay, denoted  $t_x$ , is the delay time for the signal to reach x% of  $V_{DD}$ .

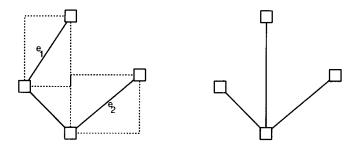

Fig. 2. Modeling of an interconnect tree as an RC tree: (a) an interconnect tree, (b) each edge is modeled as a  $\pi$ -type circuit, and (c) each edge is modeled as an RC line.

$w_e$ , and the parasitics of the interconnect as follows [7, 8]:

$$t(s_{0}, s_{i}) = \sum_{e_{r} \in Path(s_{0}, s_{i})} r_{e_{r}}(c_{e_{r}}/2 + Cap(v))$$

$$= \frac{rc_{a}}{2} \sum_{e_{r} \in Path(s_{0}, s_{i})} |e_{v}|^{2} + \frac{rc_{f}}{2} \sum_{e_{r} \in Path(s_{0}, s_{i})} \frac{|e_{v}|^{2}}{w_{e_{r}}} + rc_{a} \sum_{e_{r} \in Path(s_{0}, s_{i})} \sum_{e_{u} \in Des(e_{r})} \frac{|e_{v}| |e_{u}|}{w_{e_{t}}}$$

$$+rc_{f} \sum_{e_{r} \in Path(s_{0}, s_{i})} \sum_{e_{u} \in Des(e_{r})} \frac{|e_{v}| |e_{u}|}{w_{e_{r}}} + r \sum_{e_{r} \in Path(s_{0}, s_{i})} \sum_{u \in Sink(T_{r})} c_{u}^{s} \frac{|e_{v}|}{w_{e_{r}}},$$

$$(3)$$

where  $c_v^s = c_{s_j}^s$  if sink  $s_j$  is at node v and  $c_v^s = 0$  otherwise. The above algebraic expression allows analysis of how topology and wire widths affect Elmore delay, which leads to interconnect topology optimization algorithms such as [9, 10] and wire sizing algorithms such as [7, 11, 12].

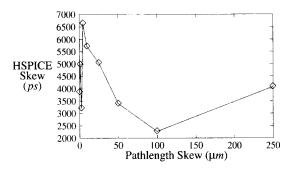

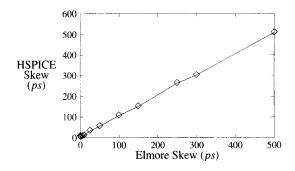

The approximation of the 50% signal delay by the Elmore delay is exact only for a symmetrical impulse response, where the mean is equal to the median [6]. Although the Elmore delay model is not accurate, it has a high degree of *fidelity*: an optimal or near-optimal solution according to the estimator is also nearly optimal according to actual (SPICE-computed [13]) delay

for routing constructions [14] and wire sizing optimization [15]. Simulations by [16] also showed that the clock skew under the Elmore delay model has a high correlation with the actual (SPICE) skew. The same study also reported a poor correlation between the path length skew and the actual skew.

In fact, one can show that the Elmore delay is the first moment of the interconnect under the impulse response. More accurate delay estimation of the interconnect can be obtained using the higher orders of the moments. In the remainder of this section, we show how to compute the higher-order moments efficiently and present several interconnect delay models using the higher-order moments.

We first define *moments* of the impulse response of a linear circuit. Let h(t) be the impulse response at a node of an interconnect (which may be an RC interconnect, an RLC interconnect, a distributed-RLC or transmission line interconnect). Let  $v_{\rm in}(t)$  be the input voltage of the linear circuit, v(t) be the output voltage of a node of interest in the circuit,  $V_{\rm in}(s)$  and V(s) be the Laplace transform of  $v_{\rm in}(t)$  and v(t), respectively; then,  $H(s) = V(s)/V_{\rm in}(s)$  is the transfer function. Applying Maclaurin expansion to the transfer function H(s), which is the Laplace transform of h(t), we obtain

$$H(s) = \int_0^\infty h(t)e^{-st} dt = \sum_{i=0}^\infty \frac{(-1)^i}{i!} s^i \int_0^\infty t^i h(t) dt.$$

(4)

The *i*th-moment of the transfer function  $m_i$  is related to the coefficient of the *i*th power of s in Eq. (4) by <sup>2</sup>

$$m_i = \frac{1}{i!} \int_0^\infty t^i h(t) \, \mathrm{d}t. \tag{5}$$

For any linear system, the normalized transfer function can also be expressed as

$$H(s) = \frac{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}{1 + b_1 s + b_2 s^2 + \dots + b_m s^m},$$

(6)

where m > n. Expanding H(s) into a power series with respect to s, we have

$$H(s) = m_0 - m_1 s + m_2 s^2 - \cdots (7)$$

The Elmore delay model is in fact the first moment  $m_1 = \int_0^\infty th(t) dt$  of the impulse response h(t). Note that  $m_1 = b_1 - a_1$  where  $a_1$  and  $b_1$  are terms in Eq. (6), and it can also be shown that the upper bound delay  $t_P$  (Eq. (1)) is in fact  $b_1$  [4].

Several approaches have been proposed to compute the moments at each node of a lumped RLC tree, where the lumped resistors and lumped inductors are floating from the ground and form a tree, and the lumped capacitors are connected between the nodes on the tree and the ground [19–21].

In the following, we present a method proposed by Yu and Kuh [21] for moment computation in an RLC tree. Consider a lumped RLC tree with n nodes. Let  $\overline{k}$  be the parent node of node k, and  $T_k$  be the subtree rooted at node k. Let  $C_k$  be the capacitance connected to node k,  $R_k$  and  $L_k$  be the

<sup>&</sup>lt;sup>2</sup> From the distribution theory, the *i*th moment of a function h(t) is in fact defined to be  $\int_0^\infty t^i h(t) dt$ . In some previous works [17, 18, 3], a variant of the moment definition  $m_i = ((-1)^i/i!) \int_0^\infty t^i h(t) dt$  was used. In this case, H(s) in Eq. (7) becomes  $H(s) = m_0 + m_1 s + m_2 s^2 + \cdots$ .

resistance and inductance of the branch between  $\overline{k}$  and k. Let  $H_k(s) = V_k(s)/V_{\rm in}(s)$  be the transfer function at node k, where  $V_k(s)$  is the Laplace transform of the output voltage at k, denoted  $v_k(t)$ . Let  $i_k(t)$  be the current flowing from  $\overline{k}$  to k; then its Laplace transform  $I_k(s)$  is given by [21]

$$I_k(s) = \sum_{j \in T_k} C_j s V_j(s). \tag{8}$$

Let  $R_{ki}$  and  $L_{ki}$  be the total resistance and inductance on the portion of the path  $Path(s_0, i)$  that is common to the path  $Path(s_0, k)$ , respectively; then, the total impedance along the common portion of paths  $Path(s_0, i)$  and  $Path(s_0, k)$  is  $Z_{ki} = R_{ki} + s \cdot L_{ki}$ . The voltage drop from root  $s_0$  to node k is [21]

$$V_{\text{in}}(s) - V_k(s) = \sum_i Z_{ki} C_i s V_i(s). \tag{9}$$

Then the transfer function  $H_k(s) = V_k(s)/V_{in}(s)$  becomes [21]

$$H_k(s) = 1 - \sum_i Z_{ki} C_i s H_i(s). \tag{10}$$

Let  $m_k^p$  be the *p*th-order moment of  $H_k(s)$ . Expanding  $H_k(s)$  and  $H_i(s)$  in Eq. (10) by the expression in Eq. (7), and equating the coefficients of powers of s, the *p*th-order moment at node k under a step input can be expressed as [21]

$$m_k^p = \begin{cases} 0 & \text{if } p = -1, \\ 1 & \text{if } p = 0, \\ \sum_i \left( R_{ki} C_i m_i^{p-1} - L_{ki} C_i m_i^{p-2} \right) & \text{if } p > 0. \end{cases}$$

(11)

Let  $C_{T_k}^p = \sum_{j \in T_k} m_j^p C_j$ , which is the total *p*th-order weighted capacitance of  $T_k$ ; then  $m_k^p$  (for p > 0) can be written recursively as [21]

$$m_k^p = \begin{cases} 0 & \text{if } k \text{ is the root } s_0, \\ m_k^p + R_k C_{T_k}^{p-1} - L_k C_{T_k}^{p-2} & \text{if } k \neq s_0. \end{cases}$$

(12)

Therefore, given the (p-1)th-order and (p-2)th-order moments, the pth-order moments of all nodes can be computed by first computing  $C_{T_k}^{p-1}$  and  $C_{T_k}^{p-2}$  in O(n) time in a bottom-up fashion. Then,  $m_k^p$  can be computed in a top-down fashion for all nodes in the interconnect tree in O(n) time. Therefore, the moments up to the pth-order of an RLC tree can be computed in O(np) time.

For moment computation of a tree of transmission lines, several works first model each transmission line as a large number of *uniform* lumped RLC segments [17,22] and then compute the moments of the resulting RLC tree. However, this approach is usually not efficient nor accurate. Kahng and Muddu [23] showed that using 10 uniform segments to approximate the behavior of a transmission line entails errors in the first and second moments of around 10% and 20%, respectively. In [23,21], the authors improve both accuracy and efficiency by considering non-uniform segmentation of the transmission line. Yu and Kuh [21] found that for exact moment computation of up to the *p*th-order, each transmission line should be modeled by  $\lfloor 3p/2 \rfloor$  non-uniform lumped RLC segments. Combining the non-uniform lumped RLC segment model by [23,21] with the moment computation algorithm by [21], the moments of a transmission line tree interconnect up to the

order of p can be computed in  $O(np^2)$  time, where n is the number of nodes in the tree. Another work of Yu and Kuh [24] computes the moments of a transmission line tree interconnect directly, without first performing non-uniform segmentation of the transmission lines. This algorithm also has a computational complexity of  $O(np^2)$ .

Higher-order moments are extremely useful for circuit analysis. In general, higher-order moments can be used to improve the accuracy of delay estimation. For example, Krauter et al. [25] proposed metrics based on the first three *central moments*, which are the moments of the distribution of the impulse response. From the distribution theory, the second central moment provides a measure of the spread of h(t) and the third central moment measures the skewness of h(t). Since the accuracy of the Elmore delay is affected by the spread and skewness of the impulse distribution, the three central moments may be used to reduce the relative errors of Elmore delay [6].

Another advantage of using higher-order moments for circuit analysis is that it can handle the inductance effect. When the operating frequencies of VLSI circuits are in the giga-hertz range and the dimension of interconnect is comparable to the signal wavelength, inductance plays a significant role in signal delay and signal integrity. An inherent shortcoming of the Elmore delay model and other simpler delay models is that they cannot handle the inductance effect.

The asymptotic waveform evaluation (AWE) method proposed by Pillage and Rohrer [17] is an efficient technique to use higher-order moments in interconnect timing analysis which can handle the inductance effect. It constructs a q-pole transfer function  $\hat{H}(s)$ , called the q-pole model,

$$\hat{H}(s) = \sum_{i=1}^{q} \frac{k_i}{s - p_i},\tag{13}$$

to approximate the actual transfer function H(s), where  $p_i$  are poles and  $k_i$  are residues to be determined. The corresponding time domain impulse response is

$$\hat{h}(t) = \sum_{i=1}^{q} k_i e^{p_i t}.$$

(14)

The poles and residues in  $\hat{H}(s)$  can be determined uniquely by matching the initial boundary conditions, denoted  $m_{-1}$ , and the first 2q-1 moments  $m_i$  of H(s) to those of  $\hat{H}(s)$  [17]. The choice of order q depends on the accuracy required but is always much less than the order of the circuit. In practice,  $q \le 5$  is commonly used.

When q is chosen to be two, it is known as the *two-pole model* [26–30]. In this model, the first three moments  $m_0$  (which is normalized),  $m_1$ , and  $m_2$  are used. A closed-form expression of  $m_2$  is given and an analytical formula relating the performance of an RLC interconnect to its topology and geometry is derived by Gao and Zhou [28]. This provides a closed-form formula for the topology optimization algorithm in [27]. However, the expression of  $m_2$  is much more complicated than that of  $m_1$  (the Elmore delay). Moreover, the method of [26, 28, 30] calculates the second moment by replacing the off-path admittance by the sum of the total subtree capacitance. This is correct only to the coefficient of s in the subtree admittance. Thus, such a method underestimates the subtree impedance. As a result, the response obtained is a lower bound of the actual response, and the delay estimate is an upper bound on the actual delay. To compute the second moment exactly, the

<sup>&</sup>lt;sup>3</sup> The three moments were also used to detect underdamping, determine the conditions of critical damping for series terminated transmission line nets, and estimate the delay of the properly terminated line [25].

admittance of off-path subtrees must be calculated correctly up to the coefficient of  $s^2$ . This was done in [19, 31, 21].

Based on the two-pole methodology, Kahng and Muddu [31] derived an analytical delay model for RLC interconnects. Consider a source driving a distributed RLC line with total resistance  $R_L$ , total inductance  $L_L$ , and total capacitance  $C_L$ . The source is modeled as a resistive and inductive impedance ( $Z_d = R_d + sL_d$ ). The load  $C_T$  at the end of the RLC line is modeled as a capacitive impedance ( $Z_T = 1/sC_T$ ). The transfer function is truncated to be [31]

$$H(s) \approx \frac{1}{1 + b_1 s + b_2 s^2},$$

(15)

where

$$\begin{split} b_1 &= R_{\rm d}C_{\rm L} + R_{\rm L}C_{\rm T} + \frac{R_{\rm L}C_{\rm L}}{2} + R_{\rm L}C_{\rm T}, \\ b_2 &= \frac{R_{\rm d}R_{\rm L}C_{\rm L}^2}{6} + \frac{R_{\rm d}R_{\rm L}C_{\rm L}C_{\rm T}}{2} + \frac{(R_{\rm L}C_{\rm L})^2}{24} + \frac{R_{\rm L}^2C_{\rm L}C_{\rm T}}{6} + L_{\rm d}C_{\rm L} + L_{\rm d}C_{\rm T} + \frac{L_{\rm L}C_{\rm L}}{2} + L_{\rm L}C_{\rm T}. \end{split}$$

The first and second moments  $m_1$  and  $m_2$  can be obtained from  $b_1$  and  $b_2$ , i.e.,  $m_1 = b_1$  and  $m_2 = b_1^2 - b_2$ . The authors separately derive the sink delay at the load  $C_T$ , denoted  $t_T$ , from the two-pole response depending on the sign of  $b_1^2 - 4b_2$  [31]:

$$t_{\rm T} = \begin{cases} K_{\rm r} \frac{m_1 + \sqrt{4m_2 - 3m_1^2}}{2} & \text{if } b_1^2 - 4b_2 > 0, \text{ i.e., real poles,} \\ K_{\rm c} \frac{2(m_1^2 - m_2)}{\sqrt{3m_1^2 - 4m_2}} & \text{if } b_1^2 - 4b_2 < 0, \text{ i.e., complex poles,} \\ K_{\rm d} \frac{m_1}{2} & \text{if } b_1^2 - 4b_2 = 0, \text{ i.e., double poles,} \end{cases}$$

where  $K_r$ ,  $K_c$ , and  $K_d$  are functions of  $b_1$  and  $b_2$  as described in [31]. The model is further extended to consider RLC interconnection trees [31] and ramp input [32].

While the methods in [31,32] used only the first two moments, Tutuianu et al. [33] proposed an explicit RC-circuit delay approximation based on the first three moments of the impulse response. The model uses the first three moments  $(m_1, m_2, \text{ and } m_3)$  to determine stable approximations of the first two dominant poles  $p_1$  and  $p_2$  of H(s). By matching the first two moments of the actual transfer function, the two residues  $k_1$  and  $k_2$  can be obtained. The explicit approximation of the delay point is a single Newton-Raphson iteration step, using the first-order delay estimate (which can be expressed in terms of the poles and residues) as the initial guess. The reader is referred to [33] for the exact expressions of  $p_1$ ,  $p_2$ ,  $k_1$ ,  $k_2$ , and the delay function.

# 2.2. Driver delay models

In interconnect-driven layout designs, gate/buffer design need to be optimized according to the interconnect load. Moreover, the design of a gate/buffer also affects interconnect design and optimization considerably. It is common that each gate or buffer has a set of implementations with varying driving capabilities. These implementations are normally characterized by input (gate) capacitance, effective output (driver) resistance, denoted  $R_{\rm d}$ , and internal delay, derived from either analytical formulas or circuit simulation.

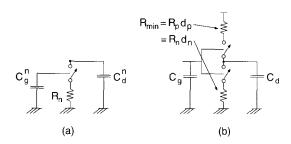

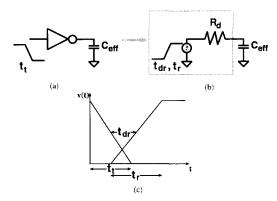

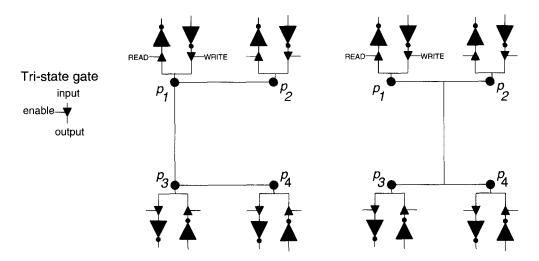

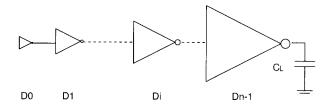

Fig. 3. A switch-level RC model of (a) an n-transistor and (b) an inverter with equal pull-up and pull-down strength by adjusting the p- and n-transistor sizes  $d_p$  and  $d_n$ , respectively.