## Simultaneous Test Pattern Compaction, Ordering and X-Filling for Testing Power Reduction

#### Ju-Yueh Lee<sup>1</sup> Yu Hu<sup>1</sup> Rupak Majumdar<sup>2</sup> Lei He<sup>1</sup>

Department of Electrical Engineering

Department of Computer Science

University of California Los Angeles

(This research is partially supported by the NSF and Actel.)

International Symposium on Quality Electronic Design, 2009

▲日▼▲□▼▲□▼▲□▼ □ ののの

#### Outline

Introduction

Preliminaries

Problem Formulation and Algorithms

◆□▶ ◆□▶ ◆ □▶ ★ □▶ = □ ● の < @

Experimental Results

Conclusions and Future Work

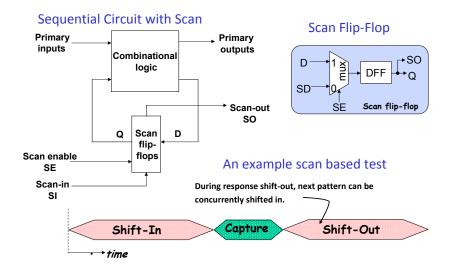

## Scan-Based Testing

◆□ > ◆□ > ◆三 > ◆三 > ・ 三 ・ のへ()・

## Increasing Testing Power Concerns

- 1. Testing power is several times higher than normal mode power

- Requirements of test time reduction

- Increasing test concurrency (Test multiple modules simultaneously)

- Increasing frequency of scan shift

- Requirements of test data volume reduction

- Compression and compaction techniques elevate circuit switching

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

- Various stressful conditions (voltage and temperature)

- Redundant switching in circuit logic during scan shift

## Increasing Testing Power Concerns

- 1. Testing power is several times higher than normal mode power

- Requirements of test time reduction

- Increasing test concurrency (Test multiple modules simultaneously)

- Increasing frequency of scan shift

- Requirements of test data volume reduction

- Compression and compaction techniques elevate circuit switching

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

- Various stressful conditions (voltage and temperature)

- Redundant switching in circuit logic during scan shift

- 2. Excessive testing power causes

- Low reliability

- Structural damage to the silicon or package

- Large voltage drop, leading to erroneous data

#### Test Power Breakdown

- 1. Average power vs. peak power

- Average power: reliability (temperature, EM)

◆□ > ◆□ > ◆臣 > ◆臣 > ─ 臣 ─ のへで

Peak power: packaging issues, IR drop

#### Test Power Breakdown

$1. \ \mbox{Average power vs. peak power}$

- Average power: reliability (temperature, EM)

- Peak power: packaging issues, IR drop

- 2. Shift power vs. capture power

- Low Frequency Shifts: Average Shift power may be a concern

- High Frequency Shifts: Peak and Average power becomes a concern

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

Capture power: Fast capture pulses in transition patterns cause Peak power (IR drop) issues

#### Test Power Breakdown

1. Average power vs. peak power

- Average power: reliability (temperature, EM)

- Peak power: packaging issues, IR drop

- 2. Shift power vs. capture power

- Low Frequency Shifts: Average Shift power may be a concern

- High Frequency Shifts: Peak and Average power becomes a concern

- Capture power: Fast capture pulses in transition patterns cause Peak power (IR drop) issues

- 3. Our approach

- considers both shift and capture power

- can be applied to both average and peak power

1. Design For Test (DFT)

- 1. Design For Test (DFT)

- 2. Automatic Test Pattern Generation (ATPG)

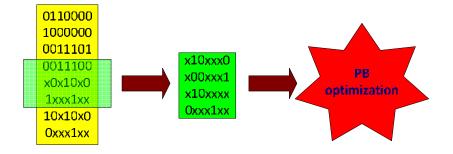

- Test patterns consist of care bits and don't-care bits, e.g., a pattern (0XXX1XX) has 5 don't care bits and 2 care bits

- ATPG decides both fill of don't-care bits and the order of a sequence of test vectors

▲日▼▲□▼▲□▼▲□▼ □ ののの

- 1. Design For Test (DFT)

- 2. Automatic Test Pattern Generation (ATPG)

- Test patterns consist of care bits and don't-care bits, e.g., a pattern (0XXX1XX) has 5 don't care bits and 2 care bits

- ATPG decides both fill of don't-care bits and the order of a sequence of test vectors

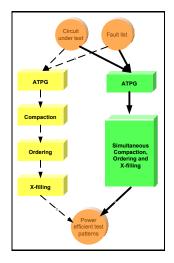

3. Three major techniques for power-aware ATPG have been proposed, i.e., compaction, ordering and X-filling

- 1. Design For Test (DFT)

- 2. Automatic Test Pattern Generation (ATPG)

- Test patterns consist of care bits and don't-care bits, e.g., a pattern (0XXX1XX) has 5 don't care bits and 2 care bits

- ATPG decides both fill of don't-care bits and the order of a sequence of test vectors

- 3. Three major techniques for power-aware ATPG have been proposed, i.e., compaction, ordering and X-filling

- 4. However, most previous researches perform the three optimizations sequentially, which may cause loss of optimality

## Major Contributions

- 1. Propose an optimal formulation for simultaneous test pattern compaction, ordering and X-filling for test mode power minimization.

- A uniform pseudo Boolean (PB)-based algorithm, applicable to both average and peak power minimization.

- Reduce power dissipation by 47%, compared to sequential approach.

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

## Pseudo-Boolean (PB) Problem

Pseudo-Boolean (PB) Constraint is an inequality

$$C_0p_0 + C_1p_1 + \cdots + C_{n-1}p_{n-1} \ge C_n,$$

where  $p_i$  is a literal and  $C_i$  is an integer coefficient for each *i*.

- An objective function is a sum of weighted literals on the same form as PB constraints.

- The Pseudo-Boolean Constraint Problem is to find a satisfying assignment to a set of PB-constraints that minimizes a given objective function.

- PB Problem can be solved by

- A generic 0-1 ILP solver, e.g., mosek

- ► A specialized SAT-based solver, e.g., minisat+

#### Test Power Modeling

Scan energy for the test vectors,  $\overrightarrow{s_1}, \cdots, \overrightarrow{s_n}$  is

$$E_{reg}(\overrightarrow{s_1},\cdots,\overrightarrow{s_m}) = \sum_{i=1}^m \sum_{j=1}^{K-1} (w_{ij}) \cdot |s_i^j - s_i^{j+1}|,$$

where  $w_{ij}$  is the weight to characterize the loading capacitance of the scan-chain registers and the weighted transition count (WTC), which has been normalized based on the K.

#### Test Power Modeling

• Scan energy for the test vectors,  $\overrightarrow{s_1}, \cdots, \overrightarrow{s_n}$  is

$$E_{reg}(\overrightarrow{s_1},\cdots,\overrightarrow{s_m}) = \sum_{i=1}^m \sum_{j=1}^{K-1} w_{ij} \cdot |s_i^j - s_i^{j+1}|,$$

• Capture energy due to the switch of two test vectors,  $\overrightarrow{s_i} \rightarrow \overrightarrow{s_{i+1}}$ , is

$$E_{cap}(\overrightarrow{s_{i}} \rightarrow \overrightarrow{s_{i+1}}) = \sum_{g \in G} C_{g} \cdot |v_{g}(\overrightarrow{s_{i}}) - v_{g}(\overrightarrow{s_{i+1}})|$$

where  $C_g$  is the loading capacitance of gate or register g in the circuit which is calculated based on Weighted Switching Activity (WSA).  $v_g(\overrightarrow{s_i})$  is the logic value at gate g under test vector  $\overrightarrow{s_i}$ .

#### Test Power Modeling

• Average test power for test vectors,  $\vec{s_1}, \cdots, \vec{s_m}$ , is

$$P(\overrightarrow{s}, \hat{m}) = \frac{E_{reg}(\overrightarrow{s_1}, \cdots, \overrightarrow{s_{\hat{m}}}) + \sum_{i=1}^{\hat{m}-1} E_{cap}(\overrightarrow{s_i} \to \overrightarrow{s_{i+1}})}{\hat{m}}$$

• Peak test power for test vectors,  $\overrightarrow{s_1}, \cdots, \overrightarrow{s_m}$ , is

$$P(\overrightarrow{s}) = \max(\max_{i} (\sum_{j=1}^{K-1} w_{ij} \cdot |s_{i}^{j} - s_{i}^{j+1}|), \max_{i} (C_{g} \cdot |v_{g}(\overrightarrow{s_{i}}) - v_{g}(\overrightarrow{s_{i+1}})|))$$

◆□▶ ◆□▶ ◆三▶ ◆三▶ - 三 - のへぐ

Problem Formulation: simultaneous test pattern compaction, ordering and X-filling (COX) for test power minimization

Given a set of test patterns  $\overrightarrow{t_1}, \cdots \overrightarrow{t_m}$ , find an ordered set of test vectors  $\overrightarrow{s_1}, \cdots \overrightarrow{s_m}$  such that

- ▶ each  $\overrightarrow{s_i} \in \{0,1\}^K$  (i.e., contains no don't-care terms),

- ▶  $\hat{m} \leq m$ ,

- ▶ fault coverage is preserved (i.e., for each  $\overrightarrow{t_i}$  there is some  $\overrightarrow{s_j}$  such that  $\overrightarrow{s_j} \dashv \overrightarrow{t_i}$ ),

the testing power dissipation objective (either overall dissipation or peak dissipation) is minimized.

## PB Formulation for COX Problem

#### COX problem

- the testing power dissipation objective is minimized.

- fault coverage is preserved,

- test vectors contain no don't-care terms,

▶

$$\hat{m} \le m$$

,

#### PB-based formulation

$\begin{array}{ll} \text{minimize} & P(\overrightarrow{s}, \widehat{m}) \\ \text{subject to} \\ \text{CNF}_{G}(\overrightarrow{s_{i}}) & \text{for } i = [1, m], \\ \bigvee_{j=1}^{\widehat{m}} (\overrightarrow{s_{j}} \dashv \overrightarrow{t_{i}}) & \text{for } i = [1, m], \\ s_{i}^{j} \in \{0, 1\} & \text{for } i = [1, m], \\ j = [1, K], \end{array}$

▲□▶ ▲□▶ ▲□▶ ▲□▶ = ● ● ●

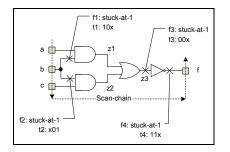

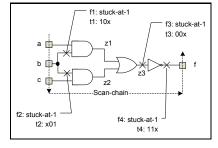

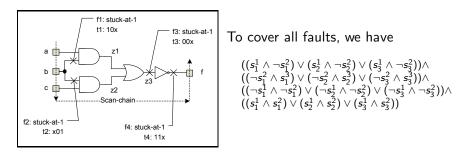

Nine 0-1 variables (literals) are needed:

$$\overrightarrow{s_1} = (s_1^1, s_1^2, s_1^3) \in \{0, 1\}^3 \overrightarrow{s_2} = (s_2^1, s_2^2, s_2^3) \in \{0, 1\}^3 \overrightarrow{s_3} = (s_3^1, s_3^2, s_3^3) \in \{0, 1\}^3$$

the objective function is

$$\begin{array}{ll} E_{reg} & = \sum_{i=1}^{3} \sum_{j=1}^{2} |s_{i}^{j} - s_{i}^{j+1}| \\ E_{cap} & = \sum_{i=1}^{2} \sum_{g \in G} C_{g} \cdot |v_{g}(\overrightarrow{s_{i}}) - v_{g}(\overrightarrow{s_{i+1}})|, \end{array}$$

where  $G = \{z_1, z_2, z_3, f\}.$

•  $|x_1 - x_2| = x_1 \oplus x_2$  can be rewritten in CNF:

$$(\neg x_1 \lor \neg x_2 \lor y) \land (x_1 \lor x_2 \lor y) \land (\neg x_1 \lor x_2 \lor \neg y) \land (x_1 \lor \neg x_2 \lor \neg y).$$

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

$$\mathsf{CNF}_G(\overrightarrow{s_i}), \text{ for } i = [1, m],$$

are as follows.

$$\begin{split} & (s_i^1 \lor \neg v_{z_1}^i) \land (s_i^2 \lor \neg v_{z_1}^i) \land (\neg s_i^1 \lor \neg s_i^2 \lor v_{z_1}^i) \land \\ & (s_i^3 \lor \neg v_{z_2}^i) \land (s_i^2 \lor \neg v_{z_2}^i) \land (\neg s_i^3 \lor \neg s_i^2 \lor v_{z_2}^i) \land \\ & (\neg v_{z_1}^i \lor v_{z_3}^i) \land (\neg v_{z_2}^i \lor v_{z_3}^i) \land (v_{z_1}^i \lor v_{z_2}^i \lor \neg v_{z_3}^i) \land \\ & (\neg v_{z_3}^i \lor \neg v_{z_4}^i) \land (v_{z_3}^i \lor v_{z_4}^i) \land \end{split}$$

where  $v_g^i$  denotes  $v_g(\vec{s_i})$ , and the above four constraints represents the characteristic function to compute the logic value of AND gates  $z_1$  and  $z_2$ , OR gate  $z_3$  and INV gate f, respectively, under test vector  $\vec{s_i}$ , for  $i = 1, \dots, 3$ .

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 三臣 - のへ(?)

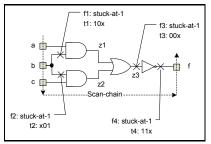

After solving the above PB constraint problem, the optimal solution returned by PB solver is

$$\overrightarrow{s_1}=(0,0,1)$$

$\overrightarrow{s_2}=(1,1,1)$

$\overrightarrow{s_3}=(1,0,0)$

▲ロ▶ ▲冊▶ ▲ヨ▶ ▲ヨ▶ ヨー のなべ

#### Peak Power Minimization

Original formulation

$$\begin{array}{ll} \text{minimize } P(\overrightarrow{s}) = & \max(\max_{i,j}(w_{ij} \cdot |s_i^j - s_i^{j+1}|), \\ & \max_i(C_g \cdot |v_g(\overrightarrow{s_i}) - v_g(\overrightarrow{s_{i+1}})|)) \\ \text{subject to} & \text{all constraints from average power minimization} \end{array}$$

#### PB-based formulation

minimize subject to

$$t \ \sum_{j=1}^{K-1} w_{ij} \cdot |s_i^j - s_i^{j+1}| \leq t \ \mathcal{C}_g \cdot |v_g(\overrightarrow{s_i}) - v_g(\overrightarrow{s_{i+1}})| \leq t$$

all other constraints from average power minimization

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

Can be solved by the binary search of t.

## Speedup By Slicing Window

▲□▶ ▲□▶ ▲□▶ ▲□▶ ▲□ ● ● ●

#### **Experimental Settings**

- ISCAD'89 benchmark circuits

- Test pattern generated by ATALANTA

- PB problem solved by minisat+

- Baseline sequential algorithm ("seq")

- Compacted by ATALANTA

- X-filled by repeated filling [Costa, IWLS'98]

- Ordered by a TSP-based algorithm [Costa, IWLS'98]

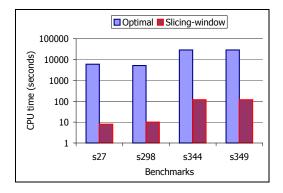

## Optimal vs. Slicing Window (SW)-Based Heuristic

- Due to the capability of PB solver, four small circuits (s27, s298, s344, s349) are tested using 20 test patterns

- The same results are obtained by the two approaches.

- SW is three orders of magnitude faster.

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

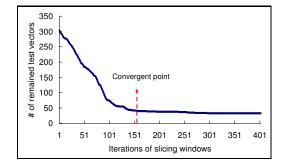

# Convergency Slicing Window

- Window size 4

- Benchmark: s298

- SW converges when 150 windows are passed, i.e. 4 iterations

(日) (同) (日) (日)

э.

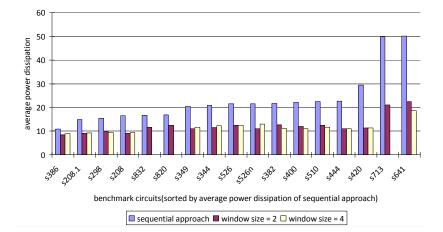

#### Power Dissipation Comparisons

▲□▶▲圖▶▲圖▶▲圖▶ 圖 のQQ

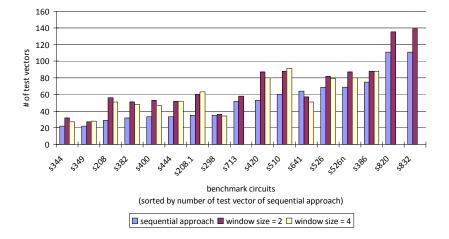

#### Test Set Size Comparisons

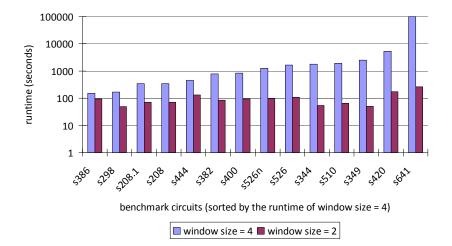

## **Runtime Comparisons**

▲ロト ▲御 ト ▲ 臣 ト ▲ 臣 ト ● の Q ()・

## Conclusions and Future Work

- A uniformed formulation for the problem of simultaneously compacting, ordering, and Xfilling to minimize power dissipation is proposed

- Our proposed approach reduces average power by 47% compared to the conventional sequential approach

- In the future, we will

- conduct experiments on average power minimization under peak power constraint

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

futhere improve the efficiency of the proposed algorithm