#include <oagFpgaVerilogSynthesis.h>

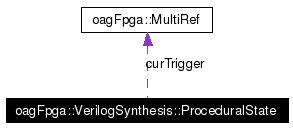

Collaboration diagram for oagFpga::VerilogSynthesis::ProceduralState:

Public Types | |

| enum | PStateType { PSTATE_SYNC, PSTATE_ASYNC } |

Public Member Functions | |

| ProceduralState () | |

Public Attributes | |

| set< oa::oaModBitNet * > | dependencies |

| map< oa::oaModBitNet *, MultiRef > | blockingAssignments |

| map< oa::oaModBitNet *, MultiRef > | nonblockingAssignments |

| bool | isRegister |

| bool | isFunction |

| map< string, FunctionVariableAssignment > | functionAssignments |

| set< oa::oaModBitNet * > | normalTriggers |

| set< oa::oaModBitNet * > | posTriggers |

| set< oa::oaModBitNet * > | negTriggers |

| set< oa::oaModBitNet * > | nonClockTriggers |

| PStateType | pStateType |

| MultiRef | curTrigger |

| map< oa::oaModBitNet *, MultiRef > | aData |

| map< oa::oaModBitNet *, MultiRef > | aLoad |

Definition at line 59 of file oagFpgaVerilogSynthesis.h.

|

|

Definition at line 76 of file oagFpgaVerilogSynthesis.h. |

|

|

Definition at line 88 of file oagFpgaVerilogSynthesis.h. |

|

|

Definition at line 84 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeIf(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 86 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeIf(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

|

Definition at line 80 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeIf(). |

|

|

Definition at line 62 of file oagFpgaVerilogSynthesis.h. |

|

|

Definition at line 67 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlockingassignment(). |

|

|

Definition at line 66 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), and oagFpga::VerilogSynthesis::synthesizeBlockingassignment(). |

|

|

Definition at line 65 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeIf(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 69 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::isAsynchronousSignal(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

|

Definition at line 72 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::isAsynchronousSignal(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 69 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 69 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::isAsynchronousSignal(), and oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 77 of file oagFpgaVerilogSynthesis.h. Referenced by oagFpga::VerilogSynthesis::synthesizeIf(). |

1.3.9.1

1.3.9.1