#include <oagFpgaVerilogDesign.h>

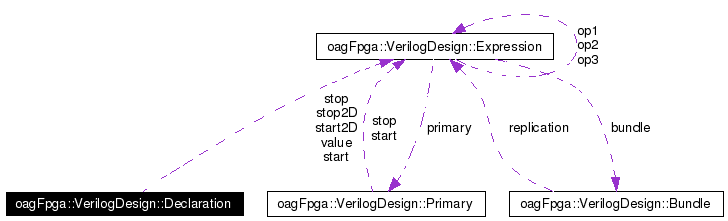

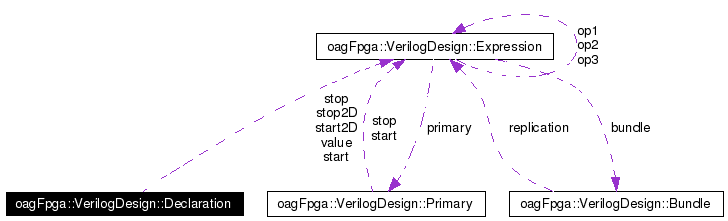

Collaboration diagram for oagFpga::VerilogDesign::Declaration:

Public Types | |

| enum | Type { UNKNOWN, INPUT, OUTPUT, WIRE, REG, INOUT, PARAMETER, SUPPLY0, SUPPLY1, TRI, WIREAND, WIREOR, TRI0, TRI1, TRIAND, TRIOR } |

Public Member Functions | |

| Declaration () | |

| ~Declaration () | |

| Destructor. | |

Public Attributes | |

| std::string | name |

| Type | type |

| Expression * | start |

| Expression * | stop |

| Expression * | start2D |

| Expression * | stop2D |

| Expression * | value |

Five declaration types are currently supported:

Definition at line 95 of file oagFpgaVerilogDesign.h.

|

|

Definition at line 99 of file oagFpgaVerilogDesign.h. |

|

|

Definition at line 123 of file oagFpgaVerilogDesign.h. |

|

|

Destructor.

Definition at line 86 of file oagFpgaVerilogDesign.cpp. |

|

|

Definition at line 98 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleNets(), and oagFpga::VerilogSynthesis::synthesizeModuleTerms(). |

|

|

Definition at line 118 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleNets(), and ~Declaration(). |

|

|

Definition at line 119 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleNets(), and ~Declaration(). |

|

|

Definition at line 118 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleNets(), and ~Declaration(). |

|

|

Definition at line 119 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), and oagFpga::VerilogSynthesis::synthesizeModuleNets(). |

|

|

Definition at line 116 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleNets(), and oagFpga::VerilogSynthesis::synthesizeModuleTerms(). |

|

|

Definition at line 121 of file oagFpgaVerilogDesign.h. |

1.3.9.1

1.3.9.1