#include <oagFpgaVerilogDesign.h>

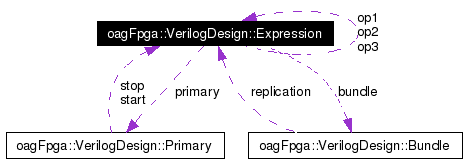

Collaboration diagram for oagFpga::VerilogDesign::Expression:

Public Types | |

| enum | Operator { UNKNOWN, PRIMARY, BUNDLE, BITWISE_AND, BITWISE_NAND, BITWISE_OR, BITWISE_NOR, BITWISE_XOR, BITWISE_XNOR, BITWISE_NOT, LOGICAL_AND, LOGICAL_NOT, LOGICAL_OR, REDUCTION_AND, REDUCTION_OR, REDUCTION_XOR, REDUCTION_NAND, REDUCTION_NOR, REDUCTION_XNOR, LESS_THAN, LESS_THAN_EQUAL, GREATER_THAN, GREATER_THAN_EQUAL, EQUAL, NOTEQUAL, IF_ELSE, LEFT_SHIFT, RIGHT_SHIFT, ADD, SUBTRACT, MULTIPLY, DIVIDE, MODULO, NEGATE } |

Public Member Functions | |

| Expression () | |

| Expression (Primary *p) | |

| Expression (Bundle *b) | |

| Expression (Expression *e1) | |

| Expression (Expression *e1, Expression *e2) | |

| Expression (Expression *e1, Expression *e2, Expression *e3) | |

| ~Expression () | |

| Destructor. | |

Public Attributes | |

| Operator | type |

| Expression * | op2 |

| Expression * | op3 |

| Expression * | op1 |

| Primary * | primary |

| Bundle * | bundle |

The expression is broken into single operations and built recursively.

Each decomposed expression may be involve one operator from the following classes:

Definition at line 379 of file oagFpgaVerilogDesign.h.

|

|

Definition at line 382 of file oagFpgaVerilogDesign.h. |

|

|

Definition at line 411 of file oagFpgaVerilogDesign.h. |

|

|

Definition at line 412 of file oagFpgaVerilogDesign.h. |

|

|

Definition at line 413 of file oagFpgaVerilogDesign.h. |

|

|

Definition at line 414 of file oagFpgaVerilogDesign.h. |

|

||||||||||||

|

Definition at line 415 of file oagFpgaVerilogDesign.h. |

|

||||||||||||||||

|

Definition at line 416 of file oagFpgaVerilogDesign.h. |

|

|

Destructor.

Definition at line 263 of file oagFpgaVerilogDesign.cpp. References type. |

|

|

Definition at line 406 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::evaluateConstantExpression(), oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), and oagFpga::VerilogSynthesis::isConstantExpression(). |

|

|

Definition at line 404 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::evaluateConstantExpression(), oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::isConstantExpression(). |

|

|

Definition at line 409 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::evaluateConstantExpression(), oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::isConstantExpression(). |

|

|

Definition at line 409 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::evaluateConstantExpression(), oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::isConstantExpression(). |

|

|

Definition at line 405 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::evaluateConstantExpression(), oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), and oagFpga::VerilogSynthesis::isConstantExpression(). |

|

1.3.9.1

1.3.9.1