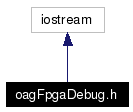

#include <iostream>Include dependency graph for oagFpgaDebug.h:

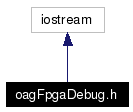

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Defines | |

| #define | DEBUG 1 |

| #define | QUIT_ON_ERROR |

| #define | QUIT_ON_INTERNAL_ERROR |

| #define | DEBUG_SYMBOL '>' |

| #define | DEBUG_PRINT(x) { cerr << DEBUG_SYMBOL << " " << x; } |

| #define | DEBUG_PRINTLN(x) { cerr << DEBUG_SYMBOL << " " << x << endl; } |

| #define | DEBUG_PRINTMORE(x) { cerr << x; } |

| #define | YU_TEST 1 |

|

|

Definition at line 6 of file oagFpgaDebug.h. |

|

|

|

|

|

Definition at line 24 of file oagFpgaDebug.h. |

|

|

Value: { \

assert(false); \

exit(0); }

Definition at line 8 of file oagFpgaDebug.h. Referenced by oagFpga::OccGraph::getTerminalDriver(). |

|

|

Value: { \

assert(false); \

cerr << "ERROR: Internal error" << endl; \

exit(0); }

Definition at line 11 of file oagFpgaDebug.h. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Definition at line 37 of file oagFpgaDebug.h. |

1.3.9.1

1.3.9.1