#include <oagFpgaVerilogDesign.h>

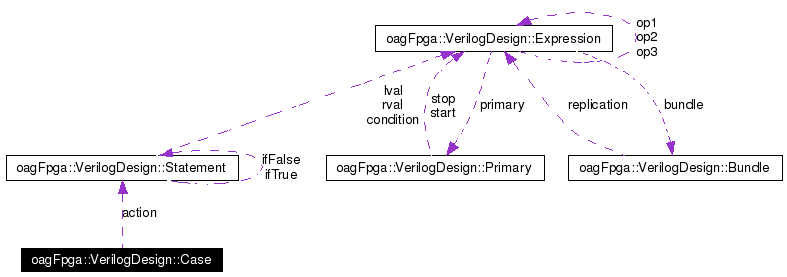

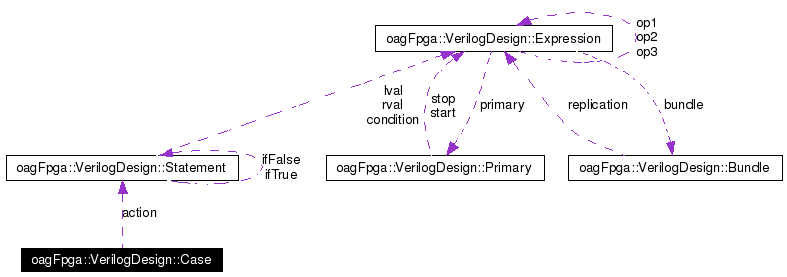

Collaboration diagram for oagFpga::VerilogDesign::Case:

Public Member Functions | |

| Case () | |

| ~Case () | |

| Destructor. | |

Public Attributes | |

| std::list< Expression * > * | conditions |

| Statement * | action |

| bool | isDefault |

Definition at line 238 of file oagFpgaVerilogDesign.h.

|

|

Definition at line 244 of file oagFpgaVerilogDesign.h. |

|

|

Destructor.

Definition at line 175 of file oagFpgaVerilogDesign.cpp. References conditions. |

|

|

Definition at line 241 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeCase(), and oagFpga::VerilogSynthesis::synthesizeCaseEasy(). |

|

|

Definition at line 240 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeCase(), oagFpga::VerilogSynthesis::synthesizeCaseEasy(), and ~Case(). |

|

|

Definition at line 242 of file oagFpgaVerilogDesign.h. Referenced by oagFpga::VerilogSynthesis::synthesizeCase(), and oagFpga::VerilogSynthesis::synthesizeCaseEasy(). |

1.3.9.1

1.3.9.1