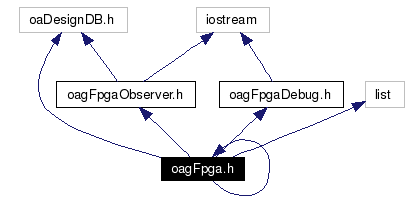

#include "oaDesignDB.h"#include "oagFpgaObserver.h"#include "oagFpgaDebug.h"#include "oagFpga.h"#include <list>Include dependency graph for oagFpga.h:

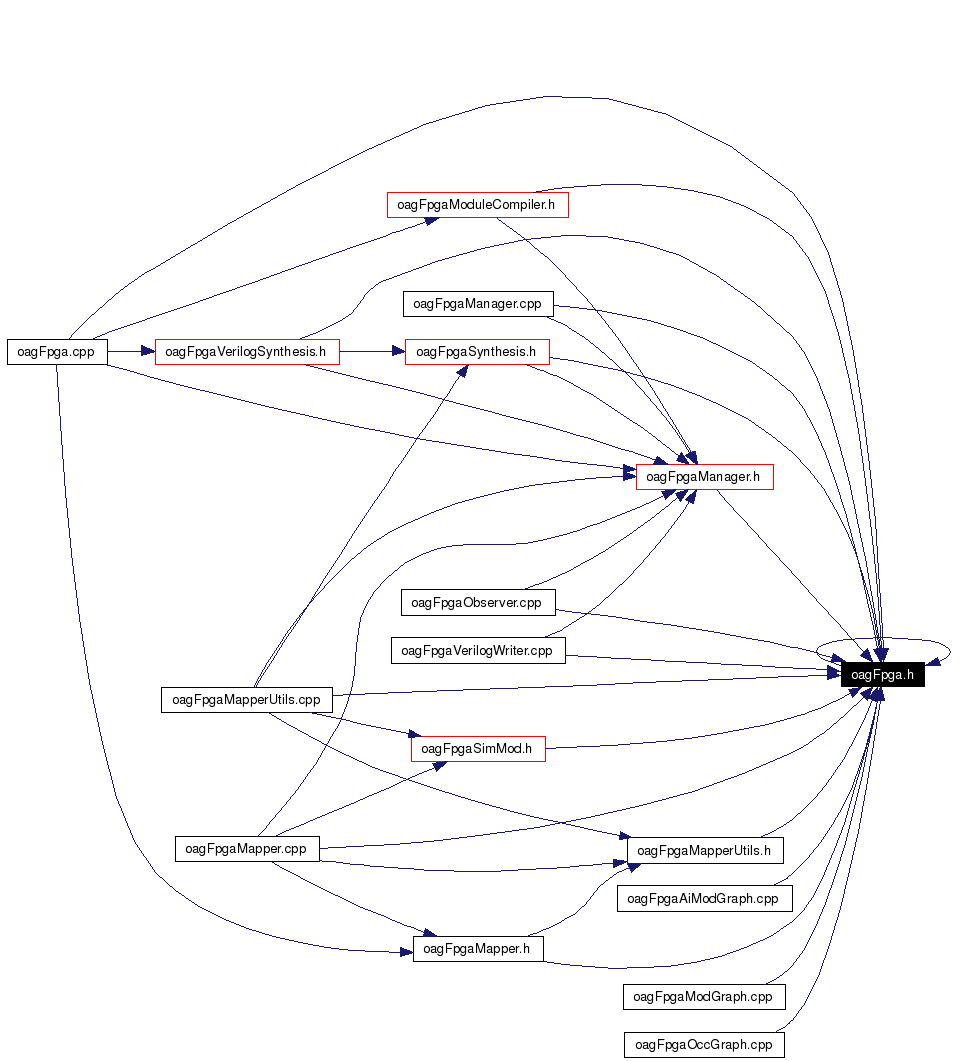

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Namespaces | |

| namespace | oagFpga |

Reading and writing functional descriptions from other formats | |

| void | writeVerilog (oa::oaLib *library, oa::oaView *view, const char *filename) |

| Write an OpenAccess library (and functional descriptions) to a Verilog file. | |

| void | writeVerilog (oa::oaDesign *design, const char *filename) |

| Write an OpenAccess design (and functional description) to a Verilog file. | |

| oa::oaModBitNet * | toBitNet (oa::oaModNet *net) |

Defines | |

| #define | oagFpga_P |

|

|

|

|

|

If the given net has multiple bits, an assertion will be generated. Definition at line 87 of file oagFpga.h. Referenced by oagFpga::ModGraph::connectEquivalentNetsInGraph(), oagFpga::AiModGraph::connectEquivalentNetsInGraph(), oagFpga::OccGraph::getAllConnections(), oagFpga::OccGraph::getInputs(), oagFpga::AiModGraph::getInputs(), oagFpga::OccGraph::getNetToBBConnection(), oagFpga::OccGraph::getOutputs(), oagFpga::ModGraph::getOutputs(), oagFpga::AiModGraph::getOutputs(), oagFpga::MapperUtils::identifyControls(), oagFpga::MapperUtils::mergeEquivalentNets(), oagFpga::Manager::print(), oagFpga::MapperUtils::removeDanglingNets(), and oagFpga::writeVerilog(). |

|

||||||||||||

|

Write an OpenAccess design (and functional description) to a Verilog file. The Verilog description will be appended to the end of the file.

Definition at line 320 of file oagFpgaVerilogWriter.cpp. References oagFpga::BBRef, oagFpga::getBaseName(), oagFpga::ModRef::ref, oagFpga::refToVerilogName(), oagFpga::toBitNet(), oagFpga::writeBBNodeToVerilog(), and oagFpga::writeNetDef(). Referenced by oagFpga::writeVerilog(). |

|

||||||||||||||||

|

Write an OpenAccess library (and functional descriptions) to a Verilog file. The Verilog descriptions will be appended to the end of the file.

Definition at line 605 of file oagFpgaVerilogWriter.cpp. References oagFpga::writePrimitiveBlackBoxs(), and oagFpga::writeVerilog(). |

1.3.9.1

1.3.9.1