#include <oagFpgaSynthesis.h>

Inheritance diagram for oagFpga::Synthesis:

Static Public Member Functions | |

| void | setLibrary (oa::oaLib *library) |

| void | setView (oa::oaView *view) |

| void | setOverwriteStructure (bool overwrite) |

| Set whether synthesis should clear and overwrite or reuse existing OA objects. Upon creating a new module, the functional description being created will always overwrite any existing functional description. | |

| void | addLeafLibrary (oa::oaLib *library) |

| void | addLeafView (const oa::oaScalarName &viewName) |

Static Protected Member Functions | |

Creating OpenAccess Structure | |

| oa::oaModule * | createModule (const string identifier) |

| Create a new module. | |

| oa::oaModScalarNet * | createScalarNet (const string identifier) |

| Creates a new scalar net or finds it if it already exists. | |

| oa::oaModBusNet * | createBusNet (const string identifier, int start, int stop) |

| Creates a new bus net or finds it if it already exists. | |

| oa::oaModTerm * | createTerm (oa::oaModNet *net, const string identifier, oa::oaTermType direction, unsigned int portPosition=oacNullIndex) |

| Create a new terminal or finds it if it already exists. | |

| oa::oaModInst * | instantiateModule (oa::oaDesign *master, const string name) |

| Instantiates a module. | |

| void | connectPort (oa::oaModInst *inst, oa::oaModNet *net, unsigned int portPosition) |

| Connects an oaModNet to an InstTerm by port position. | |

| void | connectPort (oa::oaModInst *inst, oa::oaModNet *net, const string port) |

| Connects an oaModNet to an InstTerm by name. | |

Finding Named Objects | |

| oa::oaModNet * | findNet (const string identifier) |

| Find a net, either a scalar or a bus. | |

| oa::oaModScalarNet * | findScalarNet (const string identifier) |

| Find an existing scalar net. | |

| oa::oaModBusNet * | findBusNet (const string identifier) |

| Find a bus net. | |

| oa::oaModBusNetBit * | findBusNetBit (const string identifier, const int bit) |

| Find an existing bus net bit. | |

| oa::oaModule * | findModule (const string identifier) |

| Find an existing module. | |

| bool | checkForExistenceOfDesign (oa::oaScalarName libName, oa::oaScalarName cellName, oa::oaScalarName viewName) |

Connecting OA and BB Objects | |

| void | assignMultiRef (oa::oaModBitNet *net, const MultiRef e) |

| Assigns the functionality of a net. | |

Templates for Operations definitions | |

| MultiRef | binaryOpt (RtlNode::OptType optType, MultiRef e1, MultiRef e2) |

| Return the MultiRef of a general binary operation of two MultiRefs. | |

| MultiRef | unaryBusOpt (RtlNode::OptType optType, MultiRefBus &l) |

| Returns the result of a general unary operation of a list of MultiRefs. | |

| MultiRef | binaryBusOpt (RtlNode::OptType optType, MultiRefBus &l1, MultiRefBus &l2) |

| Compares the results of a binary operation of two lists of MultiRefs. | |

| void | unaryBusInputOutputOpt (RtlNode::OptType optType, int numOutBits, MultiRefBus &result, MultiRefBus &l) |

| Returns the results (a MultiRefBuses) of a unary operation of a MultiRefBus. | |

| void | binaryBusInputOutputOpt (RtlNode::OptType optType, int numOutBits, MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the results (a MultiRefBuses) of two MultiRefBuses. | |

Primitive Logic | |

| MultiRef | notOf (MultiRef e) |

| Return the not of a MultiRef. | |

| MultiRef | orOf (MultiRef e1, MultiRef e2) |

| Return the logical OR of two MultiRefs. | |

| MultiRef | andOf (MultiRef e1, MultiRef e2) |

| Return the logical AND of two MultiRefs. | |

| MultiRef | xorOf (MultiRef e1, MultiRef e2) |

| Return the logical XOR of two MultiRefs. | |

| MultiRef | norOf (MultiRef e1, MultiRef e2) |

| Return the logical NOR of two MultiRefs. | |

| MultiRef | nandOf (MultiRef e1, MultiRef e2) |

| Return the logical NAND of two MultiRefs. | |

| MultiRef | xnorOf (MultiRef e1, MultiRef e2) |

| Return the logical XNOR of two MultiRefs. | |

| MultiRef | mux (MultiRef select, MultiRef in0, MultiRef in1) |

| Multiplexes two bits. | |

Multi-bit Comparison and Selection Operations | |

| MultiRef | reductionOr (MultiRefBus &l) |

| Returns the logical OR of a list of MultiRefs. | |

| MultiRef | reductionAnd (MultiRefBus &l) |

| Returns the logical AND of a list of MultiRefs. | |

| MultiRef | reductionXor (MultiRefBus &l) |

| Returns the logical Xor of a list of MultiRefs. | |

| MultiRef | reductionNand (MultiRefBus &l) |

| Returns the logical NAND of a list of MultiRefs. | |

| MultiRef | reductionNor (MultiRefBus &l) |

| Returns the logical NOR of a list of MultiRefs. | |

| MultiRef | reductionXnor (MultiRefBus &l) |

| Returns the logical XNOR of a list of MultiRefs. | |

| MultiRef | lessThan (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | lessThanEqual (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | equalTo (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | greaterThan (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | greaterThanEqual (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | notEqualTo (MultiRefBus &l1, MultiRefBus &l2) |

| Compares the values of two lists of MultiRefs. | |

| MultiRef | logicAnd (MultiRefBus &l1, MultiRefBus &l2) |

| logic AND of the values of two lists of MultiRefs. | |

| MultiRef | logicOr (MultiRefBus &l1, MultiRefBus &l2) |

| logic Or of the values of two lists of MultiRefs. | |

| MultiRef | logicNot (MultiRefBus &l1) |

| logic NOT of the values of a list of MultiRefs. | |

| MultiRef | mux (MultiRefBus &select, MultiRefBus &in0) |

| Multiplexes a bus DATA and a bus SEL. | |

| void | mux (MultiRefBus &result, MultiRefBus &select, MultiRefBus &in0, MultiRefBus &in1) |

| Multiplexes two buses. | |

Arithmetic Operations | |

| void | arithmeticAdd (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the sum of two MultiRefBuses. | |

| void | arithmeticSubtract (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the difference of two MultiRefBuses. | |

| void | arithmeticSubtract (MultiRefBus &result, MultiRef &negFlag, MultiRefBus &l1, MultiRefBus &l2) |

| void | arithmeticMultiply (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the product of two MultiRefBuses. | |

| void | arithmeticDivide (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the dividend of two MultiRefBuses. | |

| void | arithmeticModulo (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the remainder after division of two MultiRefBuses. | |

| void | leftShift (MultiRefBus &result, MultiRefBus &l1, MultiRefBus &l2) |

| Returns the left shifting result of (l1 << l2). | |

Sequential Elements | |

| MultiRef | latch (MultiRef enable, MultiRef in, const string name="") |

| Creates a simple latch. The latch is transparent when enable is true. | |

| MultiRef | seq (MultiRef in, MultiRef clock, const string name="") |

| Creates a generic sequential element. | |

| MultiRef | seq (MultiRef in, MultiRef clock, MultiRef aLoad, MultiRef aData, const string name="") |

| Creates a generic sequential element and annotate the asynchronous signals. | |

Constants | |

| MultiRef | constantZero () |

| Returns an MultiRef that represents a constant 0. | |

| MultiRef | constantOne () |

| Returns an MultiRef that represents a constant 1. | |

| void | zeroExpand (MultiRefBus &l1, MultiRefBus &l2) |

| Expands the smaller of two bit vectors to the length of the larger. | |

| void | multiBitConstant (MultiRefBus &result, int value, int bits=0) |

| Converts an integer value into a constant bits of the specified width. | |

Static Protected Attributes | |

State Information | |

| oa::oaNameSpace * | nameSpace = NULL |

| oa::oaLib * | currentLibrary = NULL |

| oa::oaView * | currentView = NULL |

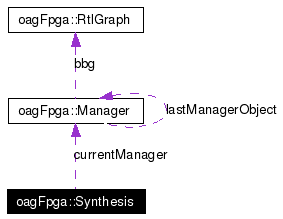

| Manager * | currentManager = NULL |

| oa::oaModule * | currentModule = NULL |

| bool | overwriteStructure = true |

| list< oa::oaLib * > | leafLibs |

| list< oa::oaScalarName > | leafViews |

| const unsigned int | NAME_LENGTH_LIMIT = 256 |

Friends | |

| class | MapperUtils |

All calls are static functions. This class is meant as a utility box for synthesizing new designs.

Definition at line 30 of file oagFpgaSynthesis.h.

|

|

Definition at line 39 of file oagFpgaSynthesis.h. |

|

|

Definition at line 41 of file oagFpgaSynthesis.h. |

|

||||||||||||

|

Return the logical AND of two MultiRefs. The necessary black box graph structures are created to represent the function. Definition at line 673 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeCase(). |

|

||||||||||||||||

|

Returns the sum of two MultiRefBuses. A ripply carry adder is built. The operands l1 and l2 must be of the same width |l1|=|l2|. /* The result will be one bit wider, |l1|+1. Definition at line 1298 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||

|

Returns the dividend of two MultiRefBuses. Builds an array divider. There is no requirement on the widths of the operands, |l1| and |l2|. The result l1/l2 will be of width |l1|; Definition at line 1346 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||

|

Returns the remainder after division of two MultiRefBuses. Builds an array divider. There is no requirement on the widths of the operands, |l1| and |l2|. The result l1%l2 will be of width |l2|; Definition at line 1361 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||

|

Returns the product of two MultiRefBuses. Builds an array multiplier. There is no requirement on the widths of the operands, |l1| and |l2|. The result l1*l2 will be of width |l1|+|l2|; Definition at line 1331 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||||||

|

|

|

||||||||||||||||

|

Returns the difference of two MultiRefBuses. Builds a ripply carry subtractor. The operands l1 and l2 must be of the same width. The result, l1-l2, will be of the same width as the operands. Definition at line 1315 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Assigns the functionality of a net. Attaches a MultiRef to a particular net. If the MultiRef refers to an oagAi::Ref, store it in the bbRefAppDef application definition. If it refers to another net, mark the two nets as equivalent. Definition at line 557 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBRef, oagFpga::bbRefAppDef, currentManager, DEBUG_PRINTLN, oagFpga::Manager::get(), oagFpga::RtlGraph::getTerminalDriver(), oagFpga::RtlGraph::isNull(), nameSpace, oagFpga::MultiRef::net, oagFpga::RtlGraph::setTerminalDriver(), and oagFpga::MultiRef::type. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleAssigns(), oagFpga::VerilogSynthesis::synthesizeModuleFunc(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

||||||||||||||||||||||||

|

Returns the results (a MultiRefBuses) of two MultiRefBuses.

Definition at line 1218 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, oagFpga::RtlGraph::binaryBusInputOutputOpt(), currentManager, currentModule, DEBUG_PRINTLN, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by arithmeticAdd(), arithmeticDivide(), arithmeticModulo(), arithmeticMultiply(), arithmeticSubtract(), and leftShift(). |

|

||||||||||||||||

|

Compares the results of a binary operation of two lists of MultiRefs. The lists must be of the same size. Definition at line 979 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, oagFpga::RtlGraph::binaryBusOpt(), currentManager, currentModule, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by equalTo(), greaterThan(), greaterThanEqual(), lessThan(), lessThanEqual(), logicAnd(), logicOr(), and notEqualTo(). |

|

||||||||||||||||

|

Return the MultiRef of a general binary operation of two MultiRefs. The necessary black box graph structures are created to represent the function. Definition at line 632 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, oagFpga::RtlGraph::binaryOpt(), currentManager, currentModule, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by andOf(), nandOf(), norOf(), orOf(), xnorOf(), and xorOf(). |

|

||||||||||||||||

|

Checks if a Design exist by opening and closing the design. This function is only a temporary wrapper for the function oaDesign::exists, because oaDesign::exists is broken.

Definition at line 94 of file oagFpgaSynthesis.cpp. Referenced by createModule(). |

|

||||||||||||||||

|

Connects an oaModNet to an InstTerm by name. The InstTerm may not preexist if the master module of the Inst has not been defined. Definition at line 780 of file oagFpgaSynthesis.cpp. References nameSpace. |

|

||||||||||||||||

|

Connects an oaModNet to an InstTerm by port position. The InstTerm may not preexist if the master module of the Inst has not been defined. Definition at line 754 of file oagFpgaSynthesis.cpp. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns an MultiRef that represents a constant 1. The MultiRef refers to a net named "tie1". This behavior is modeled after the OA to Verilog translator. Definition at line 963 of file oagFpgaSynthesis.cpp. References currentModule. Referenced by multiBitConstant(), oagFpga::VerilogSynthesis::synthesizeCase(), and oagFpga::VerilogSynthesis::synthesizeCaseEasy(). |

|

|

Returns an MultiRef that represents a constant 0. The MultiRef refers to a net named "tie0". This behavior is modeled after the OA to Verilog translator. Definition at line 943 of file oagFpgaSynthesis.cpp. References currentModule. Referenced by multiBitConstant(), oagFpga::VerilogSynthesis::synthesizeBlockingassignment(), oagFpga::VerilogSynthesis::synthesizeCase(), oagFpga::VerilogSynthesis::synthesizeCaseEasy(), oagFpga::VerilogSynthesis::synthesizeModuleAssigns(), oagFpga::VerilogSynthesis::synthesizeNonblockingassignment(), and zeroExpand(). |

|

||||||||||||||||

|

Creates a new bus net or finds it if it already exists.

Definition at line 377 of file oagFpgaSynthesis.cpp. References abs, oagFpga::Manager::bbg, currentManager, currentModule, DEBUG_PRINTLN, oagFpga::RtlGraph::getNull(), nameSpace, oagFpga::RtlGraph::newTerminal(), and oagFpga::Manager::setNetToBBConnection(). Referenced by oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleInsts(), and oagFpga::VerilogSynthesis::synthesizeModuleNets(). |

|

|

Create a new module. A design with the given identifier is either opened or created in the current library with the current view. A module with the same name is either opened or created and set as the top module. If the overwriteStructure flag is set and the design already exists, the previous version will be closed and destroyed, and a new one will be created. If the overwriteStructure flag is not set and the design already exists, any associated manager is deleted, and all references from nets to the now deleted nodes are cleared. Nothing else is touched.

Definition at line 223 of file oagFpgaSynthesis.cpp. References oagFpga::bbRefAppDef, checkForExistenceOfDesign(), currentLibrary, currentView, DEBUG_PRINTLN, oagFpga::Manager::destroy(), oagFpga::Manager::get(), oagFpga::Manager::hasManager(), oagFpga::managerAppDef, and nameSpace. Referenced by oagFpga::VerilogSynthesis::synthesizeModule(). |

|

|

Creates a new scalar net or finds it if it already exists.

Definition at line 348 of file oagFpgaSynthesis.cpp. References oagFpga::Manager::bbg, currentManager, currentModule, oagFpga::RtlGraph::getNull(), nameSpace, oagFpga::RtlGraph::newTerminal(), and oagFpga::Manager::setNetToBBConnection(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), oagFpga::VerilogSynthesis::synthesizeBlock(), oagFpga::VerilogSynthesis::synthesizeModuleInsts(), and oagFpga::VerilogSynthesis::synthesizeModuleNets(). |

|

||||||||||||||||||||

|

Create a new terminal or finds it if it already exists.

Definition at line 425 of file oagFpgaSynthesis.cpp. References nameSpace. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleTerms(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 == l2. The lists must be of the same size. Destroys their contents but does not deallocate. Definition at line 1058 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeCase(). |

|

|

Find a bus net.

Definition at line 477 of file oagFpgaSynthesis.cpp. References currentModule, and nameSpace. Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), findNet(), oagFpga::VerilogSynthesis::synthesizeBlock(), and oagFpga::VerilogSynthesis::synthesizeModuleNets(). |

|

||||||||||||

|

Find an existing bus net bit.

Definition at line 503 of file oagFpgaSynthesis.cpp. References currentModule, and nameSpace. Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::evaluateLval(). |

|

|

Find an existing module. Looks for the given name in: 1. a module in the current design (if it exists) 2. a design in the current library / view 3. a design in the leaf libraries / leaf views (if any have been provided) If the module does not exist, NULL is returned.

Definition at line 126 of file oagFpgaSynthesis.cpp. References currentLibrary, currentModule, currentView, DEBUG_PRINTLN, leafLibs, leafViews, and nameSpace. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Find a net, either a scalar or a bus.

Definition at line 537 of file oagFpgaSynthesis.cpp. References findBusNet(), and findScalarNet(). Referenced by oagFpga::VerilogSynthesis::synthesizeModuleTerms(). |

|

|

Find an existing scalar net.

Definition at line 520 of file oagFpgaSynthesis.cpp. References currentModule, and nameSpace. Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::evaluateLval(), findNet(), oagFpga::VerilogSynthesis::synthesizeBlock(), and oagFpga::VerilogSynthesis::synthesizeModuleNets(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 > l2. The lists must be of the same size. Definition at line 1087 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 >= l2. The lists must be of the same size. Definition at line 1102 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Instantiates a module.

Definition at line 323 of file oagFpgaSynthesis.cpp. References currentModule, and nameSpace. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

||||||||||||||||

|

Creates a simple latch. The latch is transparent when enable is true. The latch enable is appended as an asynchronous signal with the label "enable".

Definition at line 1393 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::bbRefAppDef, oagFpga::RtlGraph::bitSeq(), currentManager, currentModule, oagFpga::RtlGraph::getNull(), nameSpace, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by oagFpga::VerilogSynthesis::synthesizeCase(), oagFpga::VerilogSynthesis::synthesizeCaseEasy(), and oagFpga::VerilogSynthesis::synthesizeIf(). |

|

||||||||||||||||

|

Returns the left shifting result of (l1 << l2). If shift length (l2) is greater than length of operand (|l1|), result will be constant zero. Definition at line 1375 of file oagFpgaSynthesis.cpp. References binaryBusInputOutputOpt(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 < l2. The lists must be of the same size. Definition at line 1042 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 <= l2. The lists must be of the same size. Definition at line 1072 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

logic AND of the values of two lists of MultiRefs. Returns an MultiRef that is true if (l1 && l2). The lists must be of the same size. Destroys their contents but does not deallocate. Definition at line 1132 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

|

logic NOT of the values of a list of MultiRefs. Returns an MultiRef that is true if (!l). Definition at line 929 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

logic Or of the values of two lists of MultiRefs. Returns an MultiRef that is true if (l1 || l2). The lists must be of the same size. Destroys their contents but does not deallocate. Definition at line 1146 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||

|

Converts an integer value into a constant bits of the specified width. If the number of bits is zero, the function uses the smallest number of bits required. Definition at line 1803 of file oagFpgaSynthesis.cpp. References constantOne(), and constantZero(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||||||||||

|

Multiplexes two buses.

Definition at line 1690 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, oagFpga::RtlGraph::busMux(), currentManager, currentModule, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. |

|

||||||||||||

|

Multiplexes a bus DATA and a bus SEL.

Definition at line 1629 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, oagFpga::RtlGraph::busMux(), currentManager, currentModule, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. |

|

||||||||||||||||

|

Multiplexes two bits.

Definition at line 1580 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::bbRefAppDef, oagFpga::RtlGraph::bitMux(), currentManager, currentModule, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::synthesizeCaseEasy(), and oagFpga::VerilogSynthesis::synthesizeIf(). |

|

||||||||||||

|

Return the logical NAND of two MultiRefs. The necessary BB structures are created to represent the function. Definition at line 727 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Return the logical NOR of two MultiRefs. The necessary BB structures are created to represent the function. Definition at line 714 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Compares the values of two lists of MultiRefs. Returns an MultiRef that is true if l1 != l2. The lists must be of the same size. Definition at line 1117 of file oagFpgaSynthesis.cpp. References binaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

|

Return the not of a MultiRef.

Definition at line 601 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, currentManager, currentModule, oagFpga::MultiRef::net, oagFpga::MultiRef::type, and oagFpga::RtlGraph::unaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::synthesizeCase(), oagFpga::VerilogSynthesis::synthesizeIf(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

||||||||||||

|

Return the logical OR of two MultiRefs. The necessary BB structures are created to represent the function. Definition at line 687 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeCase(). |

|

|

Returns the logical AND of a list of MultiRefs.

Definition at line 882 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns the logical NAND of a list of MultiRefs.

Definition at line 894 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns the logical NOR of a list of MultiRefs.

Definition at line 905 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns the logical OR of a list of MultiRefs.

Definition at line 857 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::synthesizeCase(), oagFpga::VerilogSynthesis::synthesizeIf(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns the logical XNOR of a list of MultiRefs.

Definition at line 916 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

|

Returns the logical Xor of a list of MultiRefs.

Definition at line 870 of file oagFpgaSynthesis.cpp. References unaryBusOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), and oagFpga::VerilogSynthesis::synthesizeModuleInsts(). |

|

||||||||||||||||||||||||

|

Creates a generic sequential element and annotate the asynchronous signals.

Definition at line 1480 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::bbRefAppDef, oagFpga::RtlGraph::bitSeq(), currentManager, currentModule, DEBUG_PRINTLN, nameSpace, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. |

|

||||||||||||||||

|

Creates a generic sequential element.

Definition at line 1429 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::bbRefAppDef, oagFpga::RtlGraph::bitSeq(), currentManager, currentModule, DEBUG_PRINTLN, oagFpga::RtlGraph::getNull(), nameSpace, oagFpga::MultiRef::net, and oagFpga::MultiRef::type. Referenced by oagFpga::VerilogSynthesis::synthesizeModuleFunc(). |

|

|

Definition at line 36 of file oagFpgaSynthesis.h. |

|

|

Set whether synthesis should clear and overwrite or reuse existing OA objects. Upon creating a new module, the functional description being created will always overwrite any existing functional description. The synthesis process will also create structure (new nets, instances, terminals, etc.) as necessary. This function sets the behavior towards the OpenAccess objects that are present inside a pre-existing module. If the overwriteStructure flag is set (the default), upon synthesizing a module, the existing module will be cleared of all pre-existing OpenAccess objects. The alternative is to append functional information to pre-existing structures. This may be useful when information and structure need to be read from multiple sources (such as first loading the physical description of a cell library and then later appending the functional information for the cells). Definition at line 57 of file oagFpgaSynthesis.cpp. References overwriteStructure. |

|

|

Definition at line 37 of file oagFpgaSynthesis.h. |

|

||||||||||||||||||||

|

Returns the results (a MultiRefBuses) of a unary operation of a MultiRefBus.

Definition at line 1161 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, currentManager, currentModule, oagFpga::MultiRef::net, oagFpga::MultiRef::type, and oagFpga::RtlGraph::unaryBusInputOutputOpt(). |

|

||||||||||||

|

Returns the result of a general unary operation of a list of MultiRefs.

Definition at line 816 of file oagFpgaSynthesis.cpp. References oagFpga::MultiRef::bb, oagFpga::Manager::bbg, oagFpga::BBREF, oagFpga::bbRefAppDef, currentManager, currentModule, oagFpga::MultiRef::net, oagFpga::MultiRef::type, and oagFpga::RtlGraph::unaryBusOpt(). Referenced by logicNot(), reductionAnd(), reductionNand(), reductionNor(), reductionOr(), reductionXnor(), and reductionXor(). |

|

||||||||||||

|

Return the logical XNOR of two MultiRefs. The necessary BB structures are created to represent the function. Definition at line 740 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Return the logical XOR of two MultiRefs. The necessary BB structures are created to represent the function. Definition at line 701 of file oagFpgaSynthesis.cpp. References binaryOpt(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(). |

|

||||||||||||

|

Expands the smaller of two bit vectors to the length of the larger. The additional bits wired to constant zero. Definition at line 71 of file oagFpgaSynthesis.cpp. References constantZero(). Referenced by oagFpga::VerilogSynthesis::evaluateExpression(), oagFpga::VerilogSynthesis::synthesizeCase(), and oagFpga::VerilogSynthesis::synthesizeCaseEasy(). |

|

|

Definition at line 32 of file oagFpgaSynthesis.h. |

|

|

Definition at line 24 of file oagFpgaSynthesis.cpp. Referenced by createModule(), and findModule(). |

|

|

Definition at line 26 of file oagFpgaSynthesis.cpp. Referenced by assignMultiRef(), binaryBusInputOutputOpt(), binaryBusOpt(), binaryOpt(), createBusNet(), createScalarNet(), latch(), mux(), notOf(), seq(), unaryBusInputOutputOpt(), and unaryBusOpt(). |

|

|

Definition at line 27 of file oagFpgaSynthesis.cpp. Referenced by binaryBusInputOutputOpt(), binaryBusOpt(), binaryOpt(), constantOne(), constantZero(), createBusNet(), createScalarNet(), findBusNet(), findBusNetBit(), findModule(), findScalarNet(), instantiateModule(), latch(), mux(), notOf(), seq(), unaryBusInputOutputOpt(), and unaryBusOpt(). |

|

|

Definition at line 25 of file oagFpgaSynthesis.cpp. Referenced by createModule(), and findModule(). |

|

|

Definition at line 30 of file oagFpgaSynthesis.cpp. Referenced by findModule(). |

|

|

Definition at line 31 of file oagFpgaSynthesis.cpp. Referenced by findModule(). |

|

|

Definition at line 224 of file oagFpgaSynthesis.h. |

|

|

Definition at line 23 of file oagFpgaSynthesis.cpp. Referenced by assignMultiRef(), connectPort(), createBusNet(), createModule(), createScalarNet(), createTerm(), findBusNet(), findBusNetBit(), findModule(), findScalarNet(), instantiateModule(), latch(), and seq(). |

|

|

Definition at line 28 of file oagFpgaSynthesis.cpp. Referenced by setOverwriteStructure(). |

1.3.9.1

1.3.9.1