#include <oagFpgaVerilogSynthesis.h>

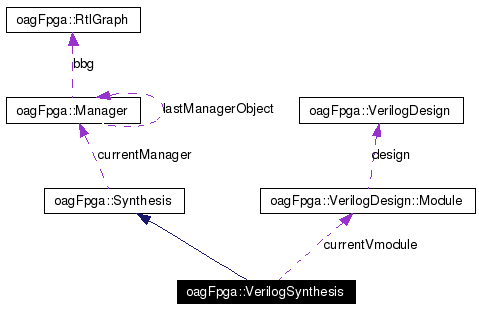

Inheritance diagram for oagFpga::VerilogSynthesis:

Static Public Member Functions | |

| void | synthesize (VerilogDesign *design) |

| Synthesize a Verilog design into OpenAccess. | |

Protected Types | |

| typedef map< string, ConstantValue > | ParameterValues |

| typedef list< LvalRef * > | LvalRefBus |

| enum | LvalType { LVAL_UNKNOWN, LVAL_UNCONDITIONAL, LVAL_CONDITIONAL, LVAL_FUNCTION } |

Static Protected Member Functions | |

| void | synthesizeModule (VerilogDesign::Module *module, list< ConstantValue > ¶meters) |

| Synthesize a Verilog module into an OpenAccess object. | |

| void | synthesizeModuleNets () |

| Synthesize the nets in a Verilog module into OpenAccess objects. | |

| void | synthesizeModuleTerms () |

| Synthesize the ports in a Verilog module into OpenAccess objects. | |

| void | synthesizeModuleAssigns () |

| Synthesize the continuous assignments in a Verilog module. | |

| void | synthesizeModuleInsts () |

| Synthesize the instantiations in a Verilog module into OpenAccess objects. | |

| void | synthesizeModuleFunc () |

| Synthesize the behavioral descriptions in a Verilog module into a BB description. | |

| void | synthesizeBehavioral (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a behavioral statement. | |

| void | synthesizeBlock (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a block statement with local variable declaration and other statements. | |

| void | synthesizeIf (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a IF statement. | |

| bool | synthesizeCaseEasy (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a CASE statement where all branch conditions are constant, true will be returned if so, false otherwise. A big MUX is inferred. | |

| void | synthesizeCase (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a CASE statement. | |

| void | synthesizeBlockingassignment (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a behavioral statement. | |

| void | synthesizeNonblockingassignment (VerilogDesign::Statement *statement, ProceduralState &state, ParameterValues *parameters) |

| Synthesize a behavioral statement. | |

| string | getParameterizedModuleName (VerilogDesign::Module *vModule, list< ConstantValue > ¶meters) |

| Creates a module name to reflect a set of parameters. | |

| void | evaluateConstantExpression (ConstantValue &result, VerilogDesign::Expression *expression, ParameterValues *parameters) |

| An error will be return if the expression is not constant. | |

| bool | isConstantExpression (VerilogDesign::Expression *expression, ParameterValues *parameters) |

| Tests if an expression is a constant or not. | |

| bool | evaluateExpression (MultiRefBus &result, VerilogDesign::Expression *expression, ProceduralState *state, ParameterValues *parameters) |

| Evaluate an expression. | |

| void | evaluateLval (LvalRefBus &result, VerilogDesign::Expression *expression, ProceduralState *state, ParameterValues *parameters) |

| Evaluate an lval. | |

| MultiRef | getContextualValue (oa::oaModBitNet *net, ProceduralState *state) |

| Return the MultiRef for a particular net, including any procedural assignment that it may have. | |

| void | appendSuffix (string &root, const string suffix) |

| Appends a suffix onto a string to construct a valid Verilog name. | |

| bool | isAsynchronousSignal (oa::oaModBitNet *net, ProceduralState *state) |

| Return true if a net is in the trigger list of the current state. | |

| string | printBitNetName (oa::oaModBitNet *n) |

Static Protected Attributes | |

Intermediate state | |

| set< string > | finishedModules |

| VerilogDesign::Module * | currentVmodule |

| The Verilog module currently being synthesized. | |

| ParameterValues * | currentParams |

| The parameters of the module currently being synthesized. | |

| map< string, Bounds > | twoDimRegisters |

All calls are static functions.

Definition at line 30 of file oagFpgaVerilogSynthesis.h.

|

|

Definition at line 140 of file oagFpgaVerilogSynthesis.h. Referenced by evaluateLval(), synthesizeBlockingassignment(), synthesizeModuleAssigns(), synthesizeModuleInsts(), and synthesizeNonblockingassignment(). |

|

|

Definition at line 40 of file oagFpgaVerilogSynthesis.h. Referenced by getParameterizedModuleName(), and synthesizeModuleInsts(). |

|

|

Definition at line 115 of file oagFpgaVerilogSynthesis.h. |

|

||||||||||||

|

Appends a suffix onto a string to construct a valid Verilog name. This routine is necessary because escaped Verilog names must end in a space.

Definition at line 4148 of file oagFpgaVerilogSynthesis.cpp. Referenced by evaluateExpression(), evaluateLval(), getParameterizedModuleName(), synthesizeBlock(), synthesizeModuleInsts(), and synthesizeModuleNets(). |

|

||||||||||||||||

|

An error will be return if the expression is not constant.

Definition at line 2425 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogDesign::Expression::bundle, DEBUG_PRINTLN, max, oagFpga::VerilogDesign::Expression::op1, oagFpga::VerilogDesign::Expression::op2, oagFpga::VerilogDesign::Expression::op3, oagFpga::VerilogDesign::Expression::primary, and oagFpga::VerilogDesign::Expression::type. Referenced by evaluateExpression(), evaluateLval(), getParameterizedModuleName(), synthesizeBlock(), synthesizeCase(), synthesizeCaseEasy(), synthesizeModule(), synthesizeModuleInsts(), and synthesizeModuleNets(). |

|

||||||||||||||||||||

|

||||||||||||||||||||

|

||||||||||||

|

Return the MultiRef for a particular net, including any procedural assignment that it may have.

Definition at line 4125 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogSynthesis::ProceduralState::blockingAssignments. Referenced by evaluateExpression(). |

|

||||||||||||

|

Creates a module name to reflect a set of parameters. Returns a string to identify a version of a module with a particular set of parameters. Currently, the parameter values are appended to the module name and delimited with the "_" character. Definition at line 71 of file oagFpgaVerilogSynthesis.cpp. References appendSuffix(), evaluateConstantExpression(), oagFpga::VerilogDesign::Module::name, oagFpga::VerilogDesign::Module::parameters, and ParameterValues. Referenced by synthesizeModule(), and synthesizeModuleInsts(). |

|

||||||||||||

|

Return true if a net is in the trigger list of the current state.

Definition at line 3034 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogSynthesis::ProceduralState::negTriggers, oagFpga::VerilogSynthesis::ProceduralState::nonClockTriggers, and oagFpga::VerilogSynthesis::ProceduralState::posTriggers. Referenced by evaluateExpression(). |

|

||||||||||||

|

Tests if an expression is a constant or not. This returns true only if all leaves of the expression are constants. Any expressions that involve nets or registers, regardless of whether the nets or regs are themselves constant will return false. Also, any expressions that involve redundancy and are functionally constant (i.e. x & !x) will not be identified and also return false. Definition at line 2641 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogDesign::Expression::bundle, oagFpga::VerilogDesign::Expression::op1, oagFpga::VerilogDesign::Expression::op2, oagFpga::VerilogDesign::Expression::op3, oagFpga::VerilogDesign::Expression::primary, and oagFpga::VerilogDesign::Expression::type. Referenced by evaluateExpression(), evaluateLval(), synthesizeCase(), and synthesizeCaseEasy(). |

|

|

Definition at line 4222 of file oagFpgaVerilogSynthesis.cpp. Referenced by synthesizeModuleFunc(). |

|

|

Synthesize a Verilog design into OpenAccess. Builds an OpenAccess module for every unparameterized Verilog module. Definition at line 39 of file oagFpgaVerilogSynthesis.cpp. References finishedModules, oagFpga::VerilogDesign::modules, oagFpga::VerilogDesign::Module::name, and synthesizeModule(). |

|

||||||||||||||||

|

Synthesize a behavioral statement.

Definition at line 2368 of file oagFpgaVerilogSynthesis.cpp. References synthesizeBlock(), synthesizeBlockingassignment(), synthesizeCase(), synthesizeCaseEasy(), synthesizeIf(), synthesizeNonblockingassignment(), and oagFpga::VerilogDesign::Statement::type. Referenced by synthesizeBlock(), synthesizeCase(), synthesizeCaseEasy(), synthesizeIf(), and synthesizeModuleFunc(). |

|

||||||||||||||||

|

Synthesize a block statement with local variable declaration and other statements.

Definition at line 1026 of file oagFpgaVerilogSynthesis.cpp. References appendSuffix(), oagFpga::VerilogDesign::Statement::begin_end, oagFpga::VerilogDesign::Statement::block, oagFpga::Synthesis::createBusNet(), oagFpga::Synthesis::createScalarNet(), DEBUG_PRINT, DEBUG_PRINTLN, DEBUG_PRINTMORE, oagFpga::VerilogDesign::Statement::declarations, evaluateConstantExpression(), oagFpga::Synthesis::findBusNet(), oagFpga::Synthesis::findScalarNet(), max, min, oagFpga::VerilogDesign::Declaration::name, oagFpga::VerilogDesign::Declaration::start, oagFpga::VerilogDesign::Declaration::start2D, oagFpga::VerilogDesign::Declaration::stop, oagFpga::VerilogDesign::Declaration::stop2D, synthesizeBehavioral(), twoDimRegisters, and oagFpga::VerilogDesign::Declaration::type. Referenced by synthesizeBehavioral(). |

|

||||||||||||||||

|

Synthesize a behavioral statement.

Definition at line 2178 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogDesign::Statement::assign, oagFpga::VerilogSynthesis::ProceduralState::blockingAssignments, oagFpga::Synthesis::constantZero(), DEBUG_PRINTLN, evaluateExpression(), evaluateLval(), oagFpga::VerilogSynthesis::ProceduralState::functionAssignments, oagFpga::VerilogSynthesis::ProceduralState::isFunction, oagFpga::VerilogDesign::Statement::lval, LvalRefBus, oagFpga::MultiRefBus, and oagFpga::VerilogDesign::Statement::rval. Referenced by synthesizeBehavioral(). |

|

||||||||||||||||

|

||||||||||||||||

|

||||||||||||||||

|

||||||||||||

|

Synthesize a Verilog module into an OpenAccess object. Builds an OpenAccess module for a Verilog module and a set of parameters. Because the parameters can significantly affect the structure of netlist, parameterization must be done at this point. The different versions of the same module with differing parameters will be identified by name. Definition at line 145 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::Synthesis::createModule(), currentParams, currentVmodule, DEBUG_PRINTLN, evaluateConstantExpression(), finishedModules, getParameterizedModuleName(), oagFpga::VerilogDesign::Module::name, oagFpga::VerilogDesign::Module::parameters, oagFpga::Manager::print(), synthesizeModuleAssigns(), synthesizeModuleFunc(), synthesizeModuleInsts(), synthesizeModuleNets(), and synthesizeModuleTerms(). Referenced by synthesize(), and synthesizeModuleInsts(). |

|

|

Synthesize the continuous assignments in a Verilog module. One of several things is done with a continuous assignment. If the assignment involves a constant or two nets, the objects are marked as equivalent nets in OpenAccess. If the assignment involves any sort of functional operator, the assign will be implemented through the attached BB graph. Definition at line 444 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogDesign::Module::assignments, oagFpga::Synthesis::assignMultiRef(), oagFpga::Synthesis::constantZero(), currentParams, currentVmodule, DEBUG_PRINTLN, evaluateExpression(), evaluateLval(), oagFpga::VerilogDesign::Assignment::lval, LvalRefBus, oagFpga::MultiRefBus, and oagFpga::VerilogDesign::Assignment::value. Referenced by synthesizeModule(). |

|

|

|

|

Synthesize the nets in a Verilog module into OpenAccess objects. Builds OpenAccess nets for a Verilog wires, integers, and regs. Definition at line 224 of file oagFpgaVerilogSynthesis.cpp. References appendSuffix(), oagFpga::Synthesis::createBusNet(), oagFpga::Synthesis::createScalarNet(), currentParams, currentVmodule, DEBUG_PRINT, DEBUG_PRINTLN, DEBUG_PRINTMORE, oagFpga::VerilogDesign::Module::declarations, evaluateConstantExpression(), oagFpga::Synthesis::findBusNet(), oagFpga::Synthesis::findScalarNet(), max, min, oagFpga::VerilogDesign::Declaration::name, oagFpga::VerilogDesign::Declaration::start, oagFpga::VerilogDesign::Declaration::start2D, oagFpga::VerilogDesign::Declaration::stop, oagFpga::VerilogDesign::Declaration::stop2D, twoDimRegisters, and oagFpga::VerilogDesign::Declaration::type. Referenced by synthesizeModule(). |

|

|

Synthesize the ports in a Verilog module into OpenAccess objects. Builds OpenAccess terms for a Verilog ports. Definition at line 379 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::Synthesis::createTerm(), currentVmodule, DEBUG_PRINTLN, oagFpga::VerilogDesign::Module::declarations, oagFpga::VerilogDesign::Port::externalName, oagFpga::Synthesis::findNet(), oagFpga::VerilogDesign::Port::internalName, oagFpga::VerilogDesign::Declaration::name, oagFpga::VerilogDesign::Module::ports, and oagFpga::VerilogDesign::Declaration::type. Referenced by synthesizeModule(). |

|

||||||||||||||||

|

Synthesize a behavioral statement.

Definition at line 2277 of file oagFpgaVerilogSynthesis.cpp. References oagFpga::VerilogDesign::Statement::assign, oagFpga::Synthesis::constantZero(), DEBUG_PRINTLN, evaluateExpression(), evaluateLval(), oagFpga::VerilogDesign::Statement::lval, LvalRefBus, oagFpga::MultiRefBus, oagFpga::VerilogSynthesis::ProceduralState::nonblockingAssignments, and oagFpga::VerilogDesign::Statement::rval. Referenced by synthesizeBehavioral(). |

|

|

The parameters of the module currently being synthesized.

Definition at line 24 of file oagFpgaVerilogSynthesis.cpp. Referenced by synthesizeModule(), synthesizeModuleAssigns(), synthesizeModuleFunc(), synthesizeModuleInsts(), and synthesizeModuleNets(). |

|

|

The Verilog module currently being synthesized.

Definition at line 23 of file oagFpgaVerilogSynthesis.cpp. Referenced by evaluateExpression(), synthesizeCase(), synthesizeCaseEasy(), synthesizeIf(), synthesizeModule(), synthesizeModuleAssigns(), synthesizeModuleFunc(), synthesizeModuleInsts(), synthesizeModuleNets(), and synthesizeModuleTerms(). |

|

|

Definition at line 25 of file oagFpgaVerilogSynthesis.cpp. Referenced by synthesize(), and synthesizeModule(). |

|

|

Definition at line 26 of file oagFpgaVerilogSynthesis.cpp. Referenced by evaluateExpression(), evaluateLval(), synthesizeBlock(), and synthesizeModuleNets(). |

1.3.9.1

1.3.9.1