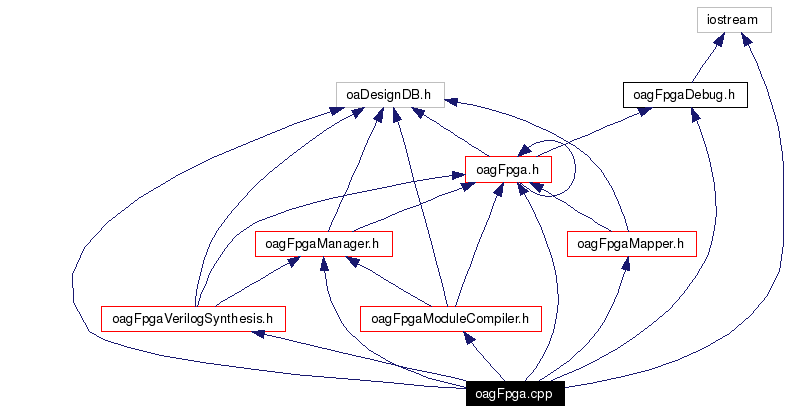

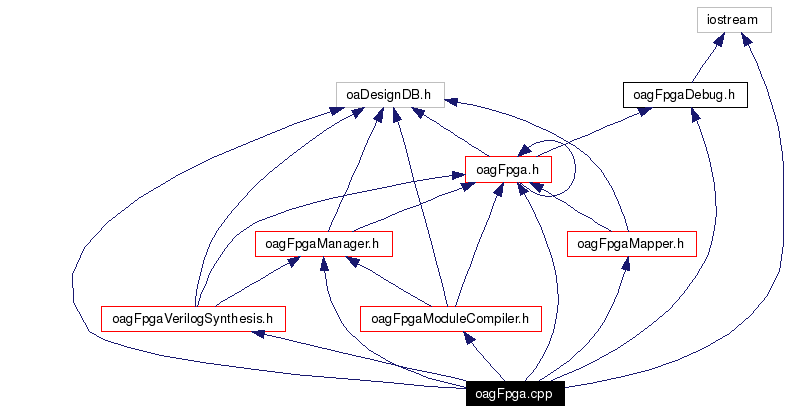

#include "oaDesignDB.h"#include "oagFpga.h"#include "oagFpgaManager.h"#include "oagFpgaMapper.h"#include "oagFpgaVerilogSynthesis.h"#include "oagFpgaModuleCompiler.h"#include <iostream>#include "oagFpgaDebug.h"Include dependency graph for oagFpga.cpp:

Go to the source code of this file.

Namespaces | |

| namespace | oagFpga |

| namespace | std |

Reading and writing functional descriptions from other formats | |

| void | readVerilog (oa::oaLib *library, const char *filename) |

| Reads a behavioral Verilog description into the netlist view. | |

| void | readVerilog (oa::oaLib *library, const oa::oaScalarName &viewName, const char *filename) |

| Reads a behavioral Verilog description. | |

| void | YuTest (oa::oaLib *curLib, oa::oaView *curView, oa::oaModule *currentModule) |

| void | lutMap (oa::oaLib *curLib, oa::oaView *curView, oa::oaDesign *targetDesign, int lutSize=4, int cutsPerNode=200, bool flatten=false, char *clockNetName=NULL, char *clockTriggerName=NULL, char *resetNetName=NULL, char *resetTriggerName=NULL, char *objectiveName="area") |

| Perform cut based technology mapping for LUT based FPGA. | |

| Observer * | observer |

| Safely casts an oaModNet* to an oaModBitNet*. | |

| oa::oaLib * | YuTestCurLib |

| oa::oaView * | YuTestCurView |

Functions | |

| int | oagFpgaVerilog_yyparse () |

| int | oagFpgaLib_yyparse () |

| void | initialize () |

| Initializes Func package. Must be called before any use. | |

Variables | |

| char * | oagFpgaVerilog_yyfilename |

| FILE * | oagFpgaVerilog_yyin |

| oagFpga::VerilogDesign * | oagFpgaVerilog_yydesign |

| FILE * | oagFpgaLib_yyin |

| oa::oaVarDataAppDef< oa::oaDesign > * | streamAppDef |

| definitions for application extensions | |

| oa::oaVoidPointerAppDef< oa::oaDesign > * | managerAppDef |

| oa::oaIntAppDef< oa::oaModBitNet > * | bbRefAppDef |

| oa::oaIntAppDef< oa::oaModBitNet > * | AiRefAppDef |

|

|

Initializes Func package. Must be called before any use. Initializes data structures for representing and manipulating functional information. The necessary AppDefs are created in the OpenAccess database. An Observer object is also created to intercept the file I/O operations on objects with functional representations. Definition at line 60 of file oagFpga.cpp. References oagFpga::AiRefAppDef, oagFpga::bbRefAppDef, oagFpga::managerAppDef, oagFpga::observer, and oagFpga::streamAppDef. |

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

Perform cut based technology mapping for LUT based FPGA.

Definition at line 200 of file oagFpga.cpp. References oagFpga::MapperUtils::addGlobalClock(), oagFpga::MapperUtils::addGlobalReset(), oagFpga::MapperUtils::createLut(), oagFpga::MapperUtils::createSeq(), oagFpga::FpgaMapper::mapUtils, oagFpga::MapperUtils::printGateUsage(), oagFpga::MapperUtils::removeDanglingNets(), oagFpga::FpgaMapper::techmapArea(), oagFpga::FpgaMapper::techmapDelay(), oagFpga::YuTestCurLib, and oagFpga::YuTestCurView. |

|

|

|

|

|

Referenced by oagFpga::readVerilog(). |

|

||||||||||||||||

|

Reads a behavioral Verilog description.

Definition at line 109 of file oagFpga.cpp. References oagFpgaVerilog_yydesign, oagFpgaVerilog_yyfilename, oagFpgaVerilog_yyin, and oagFpgaVerilog_yyparse(). Referenced by oagFpga::readVerilog(). |

|

||||||||||||

|

Reads a behavioral Verilog description into the netlist view. A view other than "netlist" can be specified with additional parameters.

Definition at line 86 of file oagFpga.cpp. References oagFpga::readVerilog(). |

|

||||||||||||||||

|

Definition at line 160 of file oagFpga.cpp. |

|

|

|

|

Definition at line 36 of file oagFpga.cpp. Referenced by oagFpga::ModuleCompiler::compileModules(), oagFpga::Manager::create(), oagFpga::Synthesis::createModule(), oagFpga::Manager::destroy(), oagFpga::Manager::get(), oagFpga::Manager::hasManager(), oagFpga::initialize(), and oagFpga::Manager::Manager(). |

|

|

|

|

|

Referenced by oagFpga::readVerilog(). |

|

|

Referenced by oagFpga::readVerilog(). |

|

|

Referenced by oagFpga::readVerilog(). |

|

|

Safely casts an oaModNet* to an oaModBitNet*.

Definition at line 42 of file oagFpga.cpp. Referenced by oagFpga::initialize(). |

|

|

definitions for application extensions

Definition at line 34 of file oagFpga.cpp. Referenced by oagFpga::initialize(), oagFpga::Observer::onFirstOpen(), oagFpga::Observer::onPostSave(), and oagFpga::Observer::onPreSave(). |

|

|

Definition at line 156 of file oagFpga.cpp. Referenced by oagFpga::lutMap(). |

|

|

Definition at line 157 of file oagFpga.cpp. Referenced by oagFpga::lutMap(). |

1.3.9.1

1.3.9.1